KAIST 전기및전자공학부 박사과정 윤기찬

#### **Session 9 Advanced Bio-Sensing Techniques**

이번 2025 IEEE VLSI의 Session 9은 Advanced Bio-Sensing Techniques라는 주제로 총 4편의 논문이 발표되었다. 다양한 형태의 bio-sensor들을 위한 센서 인터페이스가 포함된 시스템과 관련된 논문 4편이 제안되었으며, 혈류 속도를 활용한 저전력 PPG 센서 인터페이스 논문 9-2와 Electronic skin을 위한 tactile 센서 인터페이스를 제안한 9-3을 리뷰하고자 한다.

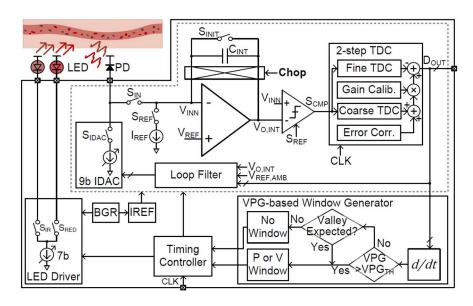

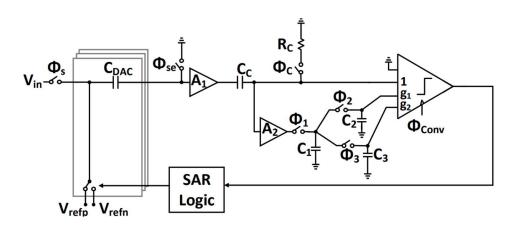

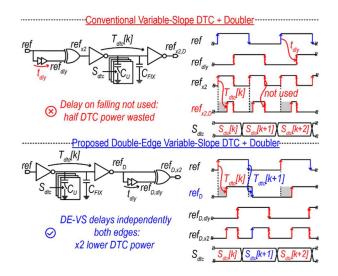

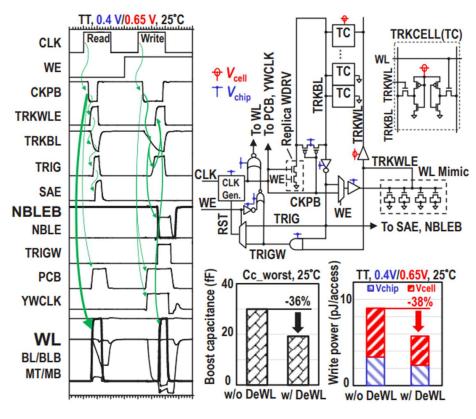

#9-2 본 논문은 POSTECH에서 발표한 연구로, 혈류 속도 (velocity of PPG, VPG) 기반의 zoomed sampling 기술을 사용하여 LED 구동을 포함한 전체 전력 소모를 크게 낮추면서도 심박수와 산소포화도 측정의 정확도를 유지한 논문이다. 기존의 저전력 PPG 센서는심박 주기 (peak-to-peak interval, PPI)를 예측하여 LED를 미리 켜는 방식을 사용하였지만, motion artifact에 취약하고, 불규칙한 심박 주기로 인해 PAV 타이밍을 놓치고, 그 때마다 새롭게 학습해야 한다는 문제를 가지고 있었다.

제안하는 구조에서는 PPG 신호의 1차 미분 신호인 VPG 신호가 각각 peak와 valley 지점에서 zero-crossing하며, systolic 구간 직후에 좁은 window안에서 최대가 되는 특성을 사용하여 안정적인 타이밍을 검출해냈다. 시스템은 LED 동작부와 correlated double-sampling 기법을 활용한 slope generator와 2-step TDC로 구성되어 있다. 먼저, 모든 current를 integration하고, chopping을 통해 correlated double-sampling을 구현하여 capacitor를 충전한 후에, 해당 charge를 discharge하면서 pulse를 만들어내고, 그 pulse를 TDC를 통해 digitization하게 된다. VPG 기반 알고리즘은 기본적으로 25Hz의 낮은 샘플링으로 동작하되, 예정된 심박 주기 구간에서는 200Hz로 zoom하여 샘플링 한다. THR은 N개의 sample의 moving average를 통해 추정하며, motion artifact 등으로 인한 error들은 제외하여 해당 영향을 최소화하였다.

결과적으로, light-to-digital converter는 0.5-20Hz에서 75.9dB의 SNDR을 가졌으며, dynamic range는 81.5dB로 측정되었다. 또한, PPI 기반 windowing에서는 PAV의 미검출률이 22.65%였던 반면, 제안한 VPG 기반 windowing에서는 이를 3.2%로 대폭 줄일 수 있었다. 전력소모는 기존 22.2µW/Ch.에서 10.4µW/Ch.으로 연속적인 sampling에 비해 53%의 전력 절감을 보여주었다. 실제 심박수 측정 오차는 0.73bpm이었으며, 산소포화도의 오차는 0.53%로 측정되어 충분한 정확도를 가짐을 검증하였다.

[그림 1] 제안하는 혈류 속도 기반 PPG 센서 인터페이스 구조

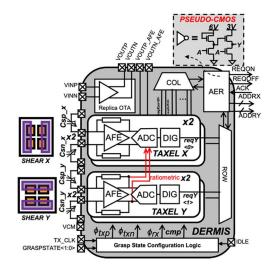

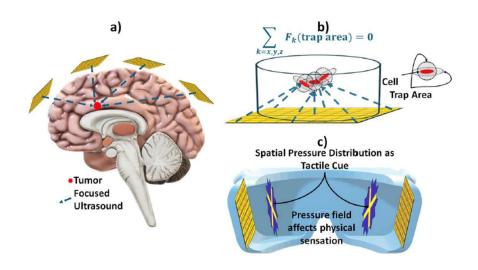

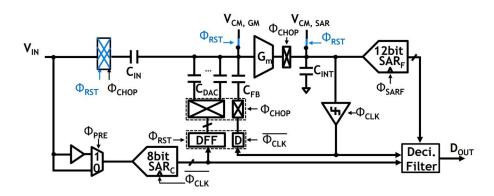

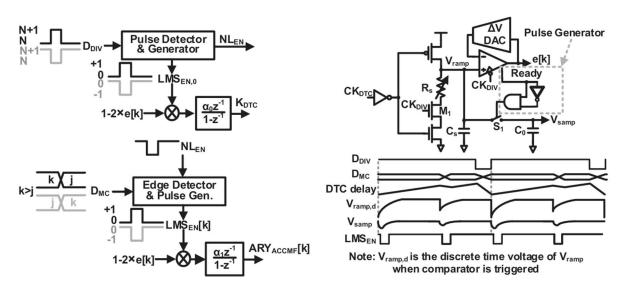

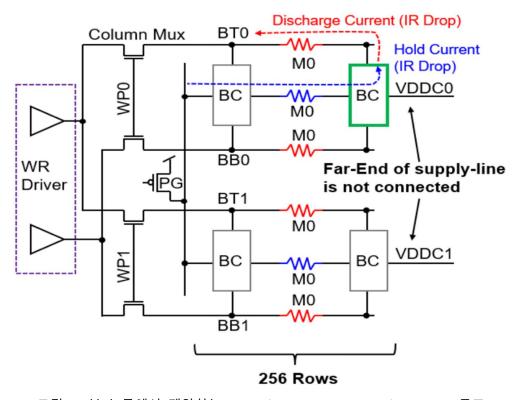

#9-3 본 논문은 KU Leuven 에서 발표한 연구로, electronic skin 을 위한 flexible fully-integrated tactile 센서 인터페이스를 제안하였다. 기존 thin-film transistor (TFT) 기반시스템에서는 off-chip sensing 에 의존하여 scaling 이 어렵거나 해상도 측면에서 한계가있어, amorphous indium gallium zinc oxide (a-IGZO) TFT 기반 공정에 differential capacitive sensor 를 integration 하여, normal 및 shear force 를 동시에 측정할 수 있는 구조를 구현하였다. 또한, 각 taxel 단위로 event-driven level-crossing ADC 를 포함시켜, slip 정보를 실시간으로 검출하되, 기존의 방식 대비 연산 및 전력 소모 부담을 크게줄였다.

[그림 2] 제안하는 electronic skin을 위한 tactile 센서 인터페이스

제안하는 per-taxel 회로는 differential capacitive-coupled IA의 입력 capacitance를 센서 입력 capacitance로 활용하여, 별도의 charge amplifier없이 구현하였으며, event-driven level-crossing ADC 기반 검출을 통해 신호의 변화를 asynchronous하게 pulse형태로 출력한다. 또한, ratio-metric mode를 지원하여, 인접한 taxel의 출력을 참고하여 shear force를 측정할 수 있어, grasp 상태에 따른 normal/shear parameter를 유연하게 재구성할 수 있다. 제작한 시스템은 600µm pitch에서 normal 및 shear force를 모두 감지할 수 있으며, 4nJ/conversion-step의 Walden FoM을 달성하여 높은 에너지 효율성을 보였다. 또한, capacitance resolution이 0.6fF<sub>rms</sub>을 달성하여, 기존 TFT 기반 readout 대비 60배의 전력소모 감소 및 400배의 면적 개선을 보여주었다.

## 저자정보

#### 윤기찬 박사과정 대학원생

● 소속 : KAIST

● 연구분야: Mixed-signal IC & Sensor interface IC

● 이메일 : ygc980215@kaist.ac.kr

● 홈페이지: https://impact.kaist.ac.kr

DGIST 전기전자컴퓨터공학과 박사과정 위정윤

#### Session C15 Biomedical Readout and Stimulation

이번 2025 IEEE VLSI Session C15에서는 바이오 센서 및 생체 자극과 관련된 주제로 총 4 편의 논문이 발표되었다.

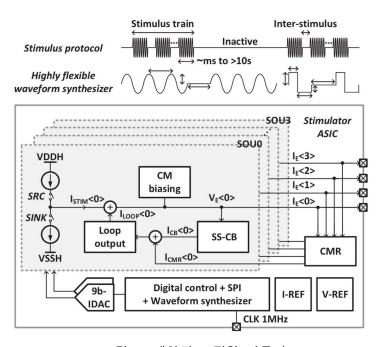

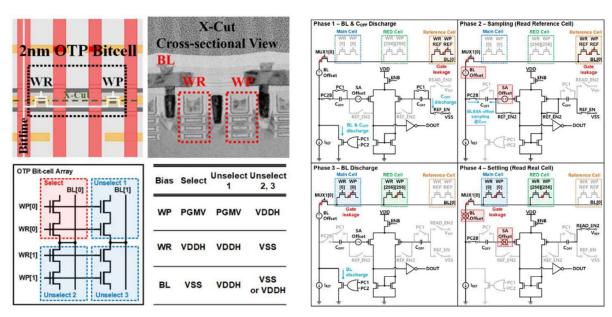

#C15-2 본 논문에서는 이식형 말초 신경 자극을 위한 고전압(HV) 자극기 ASIC을 제안하였다. 제안된 자극기는 다양한 자극 전류 파형을 지원하며, 이로 인해 발생할 수 있는 전하 축적 문제를 해결하기 위해 charge balancing(CB) 기법을 내장하였다. 유연한 자극 시스템을 구현하기 위해서는 자극기가 다중 전극을 동시에 구동할 수 있어야 하며, 10 V 이상의 신호 구동과 효율적인 CB 기술이 필수적이다. 기존 기법은 단순 biphasic 파형에서는 효과적이지만, 정현파 등 복잡한 파형에서는 처리 지연과 자극 아티팩트 문제가 발생한다. 또한 biphasic 자극에서 SOU 간 불일치를 보상하기 위해서는 전력·면적 소모가 큰 HV 블록과 큰 전극 면적이 요구되는 한계가 있었다. 제안된 ASIC은 4개의 SOU를 포함하며, 서로 다른 주파수와 진폭으로 동작할 수 있다. SRC+SINK 출력 구조와 9-bit IDAC을통해 다양한 파형을 생성할 수 있다. SOU 내부 불일치는 듀얼 루프 SS-CB 기법으로 보정하고, biphasic 파형의 위상 간의 오차는 CMR 기법으로 억제하여, 별도의 HV 블록 없이도 안정적이고 유연한 CB 성능을 달성하였다.

[그림 3] 제안된 고전압 자극기

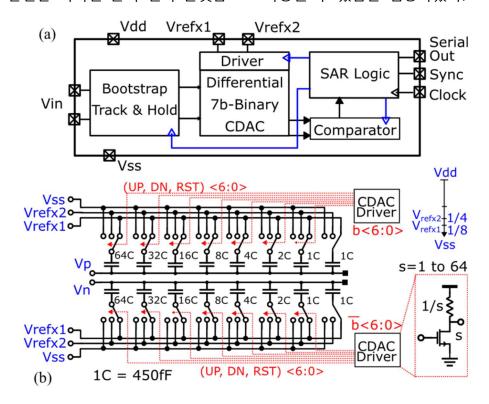

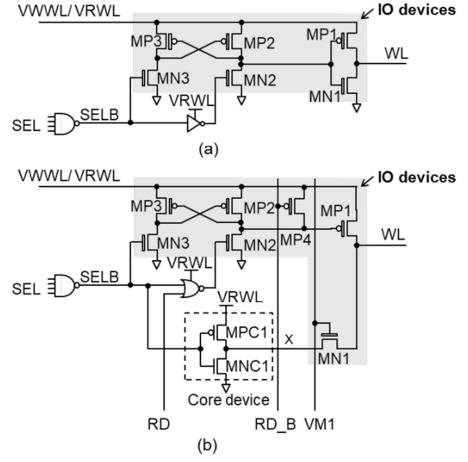

#C15-3 본 논문에서는 센서 회로와 유연 전극을 단일 기판에 통합하여 생체 신호를 디지털 출력으로 변환할 수 있는 플렉서블 바이오 전자 센서를 제안하였다. 기존 접근법은 수동 전극 또는 a-IGZO TFT 기반 전치 증폭 회로를 사용하는 방식이었으나, a-IGZO TFT 는 실리콘 대비 이동도와 신뢰성이 낮아 구현 가능한 회로가 아날로그 멀티플렉서나 단순 증폭기에 국한되었다. 이로 인해 실제 ADC는 별도의 실리콘 칩에서 구현해야 했으며, 이는 하이브리드 구조로 인한 집적도와 유연성의 한계를 초래하였다. 이러한 제약을 극복하기 위해 본 연구에서는 플렉서블 기판 상에서 직접 동작 가능한 완전 집적형 SAR ADC 시스템을 설계·검증하였다. 제안된 ADC는 실제 ECG 입력 신호를 이용해 성능을 검증하였다. Nyquist 근처(15 kHz) 입력에 대해 SNDR 44 dB를 달성했으며, 전 대역폭에서 SNDR·SNR·SFDR 특성이 안정적으로 유지되었다. 코드 밀도 분석 결과, 평균 DNL은 ±1 LSB 이내였고 INL 역시 안정적인 성능을 보였다. 전력 소모는 메인 공급 전압에서 평균 1.7 mW, 기준 전압 공급에서 약 250 nW 수준으로 측정되었다. 결론적으로, 제안된 플렉서블 SAR ADC는 기존 TFT 기반 설계 대비 성능을 크게 향상시켰으며, 실리콘 기반 ADC설계 수준에 근접하였다. 이를 통해 a-IGZO TFT 기반 유연 회로가 단순 아날로그 전치단을 넘어, 완전한 디지털 출력 센서 플랫폼으로 확장될 수 있음을 입증하였다.

[그림 4] 제안된 플렉서블 바이오 전자 센서

# 저자정보

## 위정윤 박사과정 대학원생

● 소속 : DGIST 전기전자컴퓨터공학과

● 연구분야 : Analog ICs for biomedical application

● 이메일 : wiejung@dgist.ac.kr

● 홈페이지 : http://ins.dgist.ac.kr

한국과학기술원 바이오및뇌공학과 박사과정 석동열

## **Session 24 Circuit Techniques for Biomedical Applications**

이번 2025 IEEE VLSI의 Session 24에는 Circuit Techniques for Biomedical Applications 라는 주제로 총 4편의 논문이 발표되었다. 본 세션에서는 바이오 분야의 특성에 걸맞게 주제의 다양성이 돋보였다. 삼차원 오가노이드(3D-organoid)에서 7개 모드의 다양한 실험을 수행할 수 있는 다공성 실리콘 MEA(multi-electrode array) (논문 C24-1), 폐-루프 신경신호 레코딩 목적의 저잡음 증폭기 및 Delta-Sigma ADC (논문 C24-2), 전자기 트랜스듀서 기반으로 38kbps의 데이터와 전력을 동시에 전달하는 초소형 이식형 의료기기용 무선 전력전달 및 통신 장치 (논문 C24-3), 128채널 초음파 위상 배열로부터 음향 홀로그램을 생성하는 멀티 칩 아키텍쳐 (논문 C24-4)가 소개되었다.

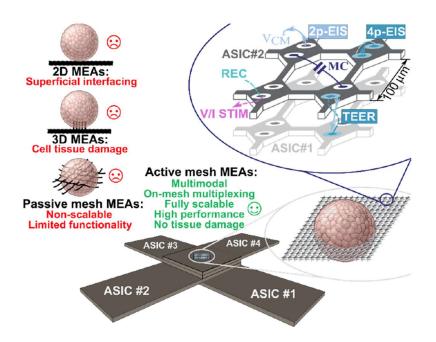

#C24-1 이 논문은 3D 오가노이드 연구를 위해 실리콘 다공성 마이크로 전극 어레이 (MEA)를 제안하고 있다. 기존 2D MEA는 평면 구조로 인해 오가노이드 내부의 입체적인 신호를 충분히 측정하기 어렵고, 전극 삽입이나 조직 절편을 만드는 방식은 조직이 손상되고, 해상도 등 신호 품질의 한계가 크다. 이를 해결하기 위해 논문에서는 두께 24μm의 얇은 실리콘을 그물구조(mesh) 형태로 가공하여 오가노이드가 자연스럽게 전극 사이를 통과하며 성장할 수 있도록 설계하였다. 각 전극은 51×51μm² 크기의 섬(island)으로 구성되며, 16×16 배열(총 256개)로 배치된다. 또한, 섬마다 저잡음 증폭기(LNA)와 능동적으로 경로 제어가 가능한 스위치 매트릭스를 탑재해, 전극 수가 늘어나도 배선 복잡성을 최소화하고 멀티플렉싱으로 효율적인 신호 처리가 가능하다.

이 시스템은 전압 기록, 전압·전류 자극, 2-point/4-point ElS(electrical impedance spectroscopy), 상호 커패시턴스, TEER 등 총 7가지 모드를 지원하여 단순 신호 기록을 넘어 조직 상태와 생리학적 변화를 종합적으로 측정할 수 있다. 300Hz~10kHz 대역에서 9.1µVrms의 저잡음과 각 섬 당 11.3µW의 저전력 특성을 달성하였으며, 심근세포 실험에서 세포 활동 전위와 세포 간 네트워크에서의 신호 전파를 정확히 기록했고, 전기자극을 통해 세포막 전기천공(electroporation)이 가능한 것도 확인했다. 이 플랫폼은 오가노이드 연구의 확장성과 정밀성을 크게 높여 신경 질환 모델링, 약물 반응 분석, 정밀의학 연구 등에 활용 가능성이 클 것으로 기대된다.

[그림 1] 3D CMOS MEA의 개념도, 브리지(bridge)에서 네 개의 단위 구조가 만나도록 설계되어 있다. 각 mesh 구조로 연결된 ASIC에 전원을 공급하고 있으며, 그 교차점이 되는 섬(island)에 7 개 모드 기능을 수행하는 전자회로와 전극부가 배치되어 있다.

[그림 2] 제안된 ASIC의 High-level 시스템 개념도

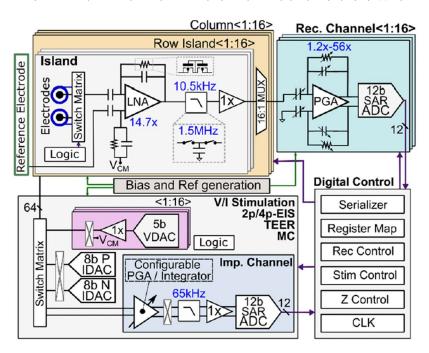

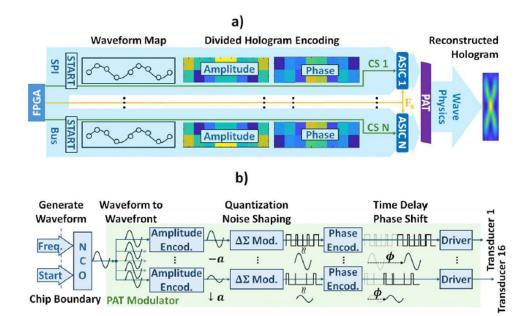

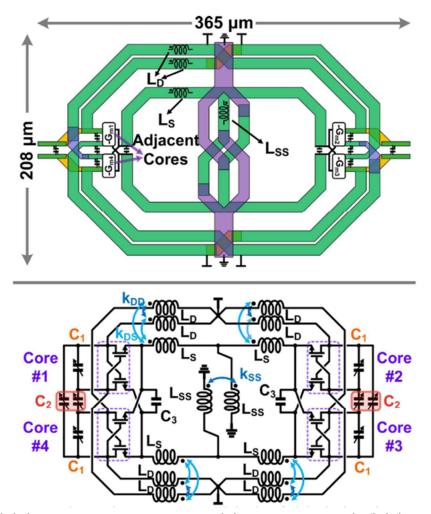

#C24-4 논문은 3 차원 음향장을 실시간으로 형성해 다양한 패턴을 만들어내는 동적 음향 홀로그램 시스템을 구현하기 위해, 확장성이 뛰어난 128 채널 멀티 칩 아키텍처를 제안한다. 기존 음향 홀로그램 기술 중 3D 프린팅 된 고정 구조물은 패턴 변경이 불가능해 정적 홀로그램만 구현할 수 있고, FPGA 와 개별 상용 칩을 사용하는 방식은 채널

수가 많아질수록 복잡성이 급격히 증가해 실시간 제어나 확장이 어렵다는 한계가 있었다. 이 논문에서는 타일 칩렛(chiplet) 구조를 통해 이러한 한계를 극복했다. 하나의 ASIC 칩이 16 채널을 제어하며, 8 개의 칩셋을 병렬로 연결해 총 128 채널을 구성하고, 필요한 경우 칩셋을 계속 추가하여 무한히 확장 가능하다. 모든 칩은 SPI 버스를 통해 중앙 FPGA 와 연결되며, 동기화된 시작 신호를 받아 위상이 완벽히 일치된 파형을 출력한다.

각 채널은 Direct Digital Synthesis(DDS)로 파형을 생성하며, 32,768 단계의 고해상도 위상 제어와 16 비트 진폭 제어를 지원한다. 특히, 32,768 단계의 시간 지연을 구현하기 위해 기존 DFF(Flip-Flop) 기반 구조 대신 SRAM 기반 디지털 지연 라인을 사용해 칩 면적을 크게 줄였다. 생성된 파형은 델타-시그마 변조기를 거쳐 1 비트 스트림으로 변환되고 H-Bridge 로 초음파 트랜스듀서를 구동한다. 128 개의 트랜스듀서를 통해 실시간으로 음향 홀로그램을 생성하였으며, 음향 홀로그램의 업데이트 속도는 344kHz 로 기존 시스템 대비 10 배 이상 향상되었다. 위상 해상도는 2π/32,768, 진폭 해상도는 16 비트로 정밀하며, 채널당 전력 소모는 12mW 로 측정되었다. 이를 통해 공중에서 입자를 포획(trap)하고 원하는 위치에 유지하는 3D 음향장을 성공적으로 형성하였다. 이 시스템은 기존 FPGA 기반 구현보다 성능과 확장성에서 크게 앞서며, 의료 분야(초음파 치료, 뇌 자극, 세포 조작), 생명과학(약물 전달, 조직 공학), VR/AR(공중 촉각 피드백) 등 다양한 첨단 응용에 활용될 수 있는 가능성을 제시한다. 결론적으로, 제안된 멀티 칩 아키텍처는 동적이고 정밀한 3D 음향 홀로그램 구현을 위한 차세대 핵심 기술로 가 평 된 다

[그림 3] 음향 홀로그램 기술의 쓰임새, a) 고강도 초음파를 이용한 뇌신경 조직 내 암 제거, b) 초음파 활용한 비침습적 세포 컨트롤, c) VR/AR 기술에서 초음파 진동을 활용한 촉각 자극 형성

[그림 4] N개의 칩렛(chiplet)을 활용하여 기본 진동의 진폭과 위상을 조절하는 경로를 개념적으로 보여주고 있는 회로도, 칩렛 당 총 16개의 트랜스듀서를 구동할 수 있다.

## 저자정보

#### 석동열 박사과정 대학원생

● 소속 : 한국과학기술원

● 연구분야 : 바이오메디컬 응용 회로설계(센서 및 신호처리)

• 이메일 : sukd10@kaist.ac.kr

KAIST 전기및전자공학부 박사과정 윤기찬

#### **Session 5 Application-Specific ADCs**

이번 2025 IEEE VLSI의 Session 5은 Application-Specific ADCs라는 주제로 총 4편의 논문이 발표되었다. 2편의 논문은 넓은 대역폭을 가지는 noise-shaping ADC이었으며, 넓은 dynamic range를 가지는 SAR ADC와 beamforming 기능이 탑재된 SAR ADC가 각각 1편씩 제안되었다. 본 review에서는 그 중 5-1, 5-2, 5-3를 리뷰하고자 한다.

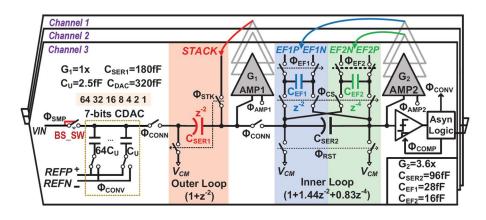

#5-1 본 논문은 University of Michigan에서 발표한 연구로, 높은 차수의 band-pass (BP) noise-shaping ADC를 구현하기 위하여 Cascaded Time-Interleaved (CaTI) NS SAR ADC 구조를 제안하였다. 기존 TI NS-SAR ADC 구조에서는 각 채널 간의 delay를 활용하여 높은 차수의 NTF를 형성할 수 있지만, 차수에 비례하여 필요한 채널 수가 증가하게 되고, 이에 따라 channel간 artifact가 심해지고, oversampling ratio 증가로 인해 대역폭이 감소한 다는 문제를 가지고 있었다. 또한, 그에 따라 NTF의 zero 최적화에 어려움을 겪었다.

제안하는 구조에서는 6차 loop filter의 구현을 outer loop에 2차 NTF를 구현하고, inner loop에 4차 NTF를 분리하여 구현함으로써,  $z^{-4}$ 의 작은 delay와 3개의 interleaving 채널을 사용하여 구현할 수 있었다. 각 loop filter는 residue voltage를 self-biasing Gm-R 구조의 증폭기를 활용하여 증폭 및 capacitor에 저장하는 형태로 구현하였으며, 각 voltage의 합산은 capacitor stacking 기법을 활용하여 각 채널의 noise-shaping 효과를 구현하였다. 또한, 증폭기의  $C_{gd}$ 에 의한 residue voltage에 error가 끼는 것을 cross-coupling capacitor를 통해 완화해주었다.

[그림 1] 제안하는 BP NS-SAR ADC 구조

결과적으로, 제안하는 구조는 1.4 GS/s에서 동작하여 175 MHz 대역폭에서 59.7 dB SNDR과 77.5 dB SFDR을 기록하였다. 전력 소모는 3.38 mW이었으며, 그에 따라 167 dB의 FoMs를 달성하였다. 특히, 공급 전압 변화나 온도 변화에 대해 성능 변화가 3~5 dB 이내로 유지되는 등, 캘리브레이션 없이도 안정적인 동작을 보여주었다.

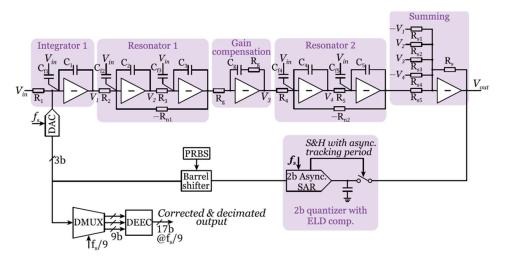

#5-2 본 논문은 Delft University of Technology에서 발표한 연구로, FMCW radar 시스템을 위한 넓은 대역폭을 가지는 고선형성 CT DSM 구조를 제안하였다. 이를 만족하면서 CT DSM의 에너지 효율성을 높이기 위해서는 높은 차수의 NTF와 multi-bit quantizer를 필요로 하지만, 기존 Butterworth 기반 NTF는 in-band noise suppression 효과가 제한적이며, flash quantizer의 높은 전력 소모 및 offset calibration 등이 에너지 효율성을 제한하였다.

제안하는 구조에서는 out-band에서 추가적인 1차 roll-off를 발생시켜, 일반적인 NTF에 비해 9.5dB 향상을 보였으며, 1개의 integrator와 2개의 resonator를 이용하여 구현하였다. 또한, NTF의 개선을 통해 sampling 주파수를 낮출 수 있어, 2-bit SAR quantizer의 사용이용이 해져 offset calibration이 추가로 필요하지 않은 구조를 제안하였다. 또한, 첫번째 integrator의 에너지 효율성을 위하여 1-stage inverter 기반 증폭기로 구현하였으며, 부족한 DC gain을 보정하여 stability를 만족하도록 하였다. 결과적으로, 제안하는 CT DSM은 49.5mW를 소모하며 100MHz의 대역폭에서 74.5dB의 SNDR과 122Db의 SFDR을 확보하였으며, THD는 약 -100.1dBc로 측정되어 FMCW radar 시스템에의 적용 가능성을 보여주었다. 또한, 167.6dB의 Schreier FoM을 달성하며 기존 CT DSM 대비 약 5.6dB 더 좋은 성능을 달성하였다.

[그림 2] 제안하는 FMCW radar 시스템을 위한 CT DSM 구조

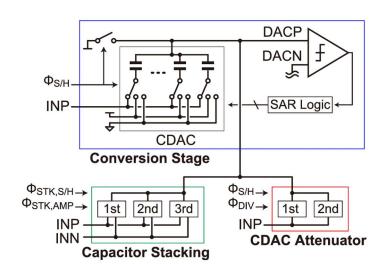

#5-3 본 논문은 University of Tokyo에서 발표한 연구로, input range를 가변적으로 조절할수 있는 8-bit 100MS/s SAR ADC를 제안하였다. 다양한 센서 인터페이스 등에서는 높은 dynamic range 및 저전력 동작을 요구하고 있지만, high-resolution ADC를 사용하는 구조 및 variable gain amplifier를 사용한 VGA+ADC구조 모두 높은 전력 소모 및 대역폭이 제한되는 문제를 가지고 있었다.

제안하는 구조에서는 passive switched-capacitor 기반의 range 조절 회로를 SAR ADC의 CDAC과 통합하여 설계하였다. 두 개의 attenuation divider를 SAR CDAC에 추가하고, bottom plate sampling을 통해 SAR ADC를 구현함으로써, input 크기에 따라 적합한 resolution을 제공할 수 있었다. 하지만, input의 크기가 작을 때에는 quantization noise가 아닌 좁은 range를 quantization함에 따라 comparator의 noise가 증가하게 되고, 이를 보완하기 위하여 input을 서로 다른 capacitor에 sample한 후에 capacitor stacking 기술을 통해 passive gain으로 comparator noise를 suppression하였다. 결과적으로 35dB를 가변 할 수 있는 입력 범위를 구현하였다. 결과적으로 0.599mW의 전력을 소모하면서 48.7dB의 SNDR과 65.6dB의 SFDR을 달성하였으며, 입력 신호 크기가 0dBFS로부터 - 35dBFS까지 변화하더라도 40dB 이상의 SNDR이 유지되어 76.5dB의 dynamic range를 확보하였다. Active VGA 없이 passive 소자들로 구성되어 별도의 calibration 없이도 PVT variation에 강인한 특성을 보여주었으며, 185.7dB의 높은 dynamic range 기반 Schreier FoM을 달성하였다.

[그림 3] 제안하는 입력범위 조절 가능한 SAR ADC 구조

# 저자정보

## 윤기찬 박사과정 대학원생

● 소속 : KAIST

• 연구분야 : Mixed-signal IC & Sensor interface IC

• 이메일 : ygc980215@kaist.ac.kr

● 홈페이지 : https://impact.kaist.ac.kr

KAIST 전기및전자공학부 박사과정 윤기찬

#### **Session 32 High-Resolution ADCs**

이번 2025 IEEE VLSI의 Session 32는 High-Resolution ADCs라는 주제로 총 5편의 논문이 발표되었다. Pipelined-SAR 및 다양한 noise-shaping ADC 구조들이 제안되었으며, 그 중 CT Zoom ADC의 residue leakage issue를 해결한 32-2, kT/C noise-shaping 기법을 제안한 32-3, 그리고 0-1-0 MASH 구조에서 driving 난이도 및 noise 문제를 해결한 32-4 논문을 리뷰하고자 한다.

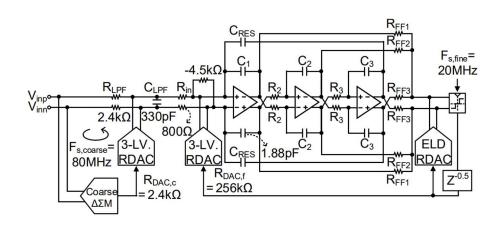

#32-2 본 논문은 연세대학교에서 발표한 연구로, 저전력으로 넓은 dynamic range 를 확보할 수 있는 CT Zoom ADC 구조를 제안한다. 기존 Zoom ADC 는 coarse SAR ADC 와 fine ADC 로 이루어지는데, 높은 해상도를 가져가기 위해서는 coarse DAC 의 resolution 이 높아져야 하지만 non-linearity 가 문제된다. 또한, offset 및 mismatch 보정 회로 등의 복잡성이 증가하는 문제가 발생한다.

제안하는 구조에서는 coarse 와 fine DSM 사이에 inter-stage 1st-order LPF를 추가하여 anti-aliasing 효과 및 고주파 noise 성분을 억제함으로써, intrinsically linear 한 1.5-bit DAC 을 사용하여 6bit 이상의 resolution 개선 및 linearity 개선을 할 수 있었다. 또한, active RC integrator 의 offset 및 noise 를 최소화하기 위하여 negative-R 기법 및 chopping을 적용하여 ADC를 구성하였다.

[그림 1] 제안하는 CT Zoom DSM 구조

Coarse loop 은 80MS/s 로 동작하며, fine loop 은 20MS/s 으로 동작하여 250kHz 의 대역폭에서 SNDR 91.2dB, SFDR 101.4dB 및 92.7dB 의 dynamic range 를 달성하였으며, 전력 소모는 약 392μW 였다. 이는 기존 구조 대비 약 12.5 배의 대역폭 확장을 달성하였으며, 180.7dB 의 FoM<sub>DR</sub>, 179.2dB 의 FoM<sub>SNDR</sub>을 달성하여, 100kHz 이상 대역폭을 가지는 CT ADC 중 가장 높은 FoM<sub>SNDR</sub>을 보여주었다.

#32-3 본 논문은 Tsinghua University 에서 발표한 연구로, 기존 kT/C noise cancellation 기술의 한계를 극복하는 kT/C noise-shaping 기법을 제안한다. 고해상도 NS-SAR ADC는 kT/C noise 에 해상도가 제한되는데, 이를 해결하기 위해서는 CDAC 의 크기를 키워야 한다. 하지만, input 및 reference driver 의 전력 소모가 증가하게 된다. 이러한 문제를 해결하기 위해 kT/C noise cancellation 방식이 제안되었지만, 대역폭이 넓은 증폭기를 필요로 하여 전력 소모가 크고, noise aliasing을 유발하는 문제를 가지고 있다.

제안하는 구조에서는 저주파 대역에서만 kT/C noise 를 추출 및 shaping 하는 방식을 차용하였다. Noise 를 추출하는 capacitor 를 초기화하지 않고, 계속해서 integration 및 LPF 하면서, 저주파 성분을 효과적으로 억제하는 동시에 기존 방식 대비 증폭기의 대역폭 요구를 3.6 배 완화할 수 있으며, driver들의 noise 요구사항도 낯출 수 있다. 또한, 필요로 하는 추출 시간을 줄일 수 있기 때문에 증폭기의 전력 소모를 크게 줄일 수 있다. 회로 관점에서는 150fF 의 CDAC 및 110fF 의 kT/C noise 추출 capacitor 를 사용하였으며, passive integrator 를 사용하여 2 차 NTF 를 구현하였다. 제작된 프로토타입은 40MHz 샘플링 주파수와 OSR 16 에서 85.8dB SNDR, 105.4dB SFDR 을 달성하였으며, 906µW 만을 소모하였다. 최종적으로 86dB 의 dynamic range 를 달성하여, 177.2dB 의 Schreier FoM 을 얻을 수 있었다.

[그림 2] 제안하는 kT/C noise-shaping SAR ADC 구조

#32-4 본 논문은 Tsinghua University 에서 발표한 연구로, 기존 two-step SAR ADC 와 CT zoom ADC 의 한계를 극복하는 multi-rate MASH 0-1-0 ADC 를 제안한다. Two-step SAR 은 높은 해상도를 얻을 수 있지만 residue amplifier 의 전력 소모가 크며, CT zoom ADC 는 kT/C noise 문제를 피하고 에너지 효율이 좋지만 높은 OSR 로 인해 대역폭이 제한된다.

제안하는 구조에서는 8b coarse SAR ADC, 1b incremental CT DSM, 그리고 12b fine SAR ADC를 결합한 multi-rate MASH 0-1-0 구조를 사용한다. coarse SAR은 oversampling 으로 MSB를 처리하고 residue voltage를 생성하며, CTDSM은 이를 적분하여 noise를 suppression 하며, fine SAR ADC는 Nyquist rate 에서 동작하여 전체 전력 소모를 줄일 수 있었다. 또한, capacitive input network를 도입하여 입력 드라이버 부담을 줄이고 thermal noise를 최소화하였으며, dead-band switch-embedded Gm-C integrator를 구현하여 CT integrator의 non-linearity와 noise를 억제하였다. 프로토타입은 1 MHz 샘플링 및 500kHz 대역폭에서 94.4 dB SNDR, 95.5 dB DR를 달성하였고 793µW만을 소모하여 182.3 dB Schreier FoM을 달성하여, 높은 에너지 효율성을 보여주었다.

[그림 3] 제안하는 multi-rate MASH ADC 구조

#### 저자정보

#### 윤기찬 박사과정 대학원생

● 소속 : KAIST

• 연구분야: Mixed-signal IC & Sensor interface IC

• 이메일 : ygc980215@kaist.ac.kr

• 홈페이지 : https://impact.kaist.ac.kr

DGIST 전기전자컴퓨터공학과 박사과정 위정윤

## **Session C8 High-Speed ADCs**

이번 2025 IEEE VLSI Session C8에서는 High-speed ADCs를 주제로 총 4편의 논문이 발표되었으며, 기존 ADC의 한계를 극복하기 위한 다양한 새로운 구조의 ADC가 제안되었다.

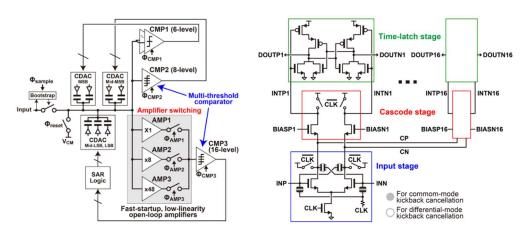

#C8-1 본 논문에서는 차세대 무선 통신을 위한 고성능 ADC 요구를 충족하기 위해 amplifier-switching subranging 구조를 적용한 14비트, 560 MS/s ADC를 구현하였다. 기존 파이프라인 ADC가 속도와 해상도 사이의 트레이드오프 문제를 겪는 것과 달리, 제안된 구조는 정밀 증폭기 없이도 고속·고해상도 동작을 동시에 달성한다. 이를 위해 단일 입력 쌍으로 16레벨 양자화를 수행할 수 있는 time-latch 기반 multi-threshold 비교기를 도입하여 입력 기준 잡음을 줄이고 전력 소모를 낮췄다. 또한 단일 입력쌍을 공유해 다중 임계값을 구현함으로써 입력 기준 잡음·입력 용량·kickback 노이즈를 동시에 억제하였다. ADC는 총 5단계 변환 구조로 동작하며 CMP1~CMP3을 통해 고해상도를 확보한다. AMP1~AMP3는 단계별 잡음 요구에 맞춰 동작하여 전력 소모를 줄이고 CDAC으로의 kickback 노이즈를 차단한다. 특히 AMP1과 AMP2의 오차는 CDAC redundancy로 보정할수 있어 저전력 인버터 기반 증폭기 적용이 가능하다. 이러한 설계를 통해 subranging ADC의 해상도를 기존 한계를 넘어 10비트 이상으로 확장할 수 있음을 보였다.

[그림 1] 제안된 14-bit subranging ADC와 multi-threshold 비교기

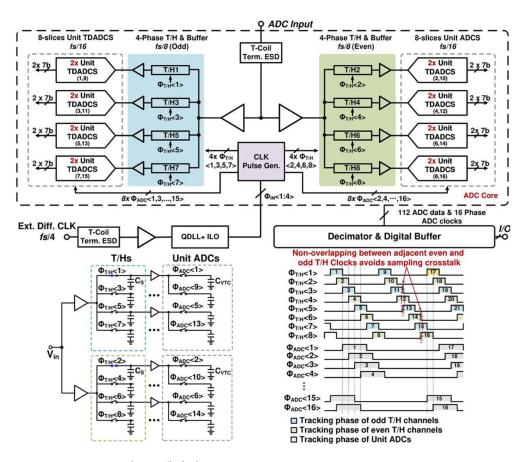

#C8-2 본 논문에서는 7비트, 16-way time-interleaved TDADC를 제안하였다. TDADC는 디지털 특성을 갖는 타이밍 신호를 활용하여 첨단 CMOS 공정과의 호환성이 높고 합성 가능한 구현이 가능하지만, 기존 구조는 전압-시간 변환기(VTC)의 왜곡과 TDC 복잡성으로

인해 성능이 제한된다. 이를 해결하기 위해, 제안된 단위 ADC는 MOS 캐패시터 기반 3차 비선형 보상 VTC와 phase interpolation 기능을 갖춘 3입력 time comparator(I-TCMP)를 도입하였다. 이로써 보정 과정 없이도 동작 가능하며, 필요한 phase interpolator 수를줄일 수 있다. 단위 ADC는 Verilog 합성과 자동화된 디지털 place-and-route 기법으로 구현되었으며, 표준 셀과 맞춤형 아날로그 셀(VTC, I-TCMP)을 기반으로 자동 레이아웃이생성된다. 16개의 단위 ADC를 time-interleaving 구조로 통합한 결과, 46 GS/s 동작 속도, Nyquist 입력에서 78 fJ/conv.-step 에너지 효율, 20.1 GHz 3 dB 대역폭, 0.085 mm² 면적을 달성하였다. 결론적으로, 제안된 TDADC는 기존 구조의 한계를 극복하고 보정 과정 없이도 고속·저전력 동작을 달성하였으며, 대규모 time-interleaving 구조에도 효율적으로 확장 가능함을 보였다. 이를 통해 차세대 초고속 통신 및 고성능 데이터 변환 응용에 적합한 설계 방법임을 입증하였다.

[그림 2] 제안된 Time-interleaved time-domain ADC

# 저자정보

## 위정윤 박사과정 대학원생

● 소속 : DGIST 전기전자컴퓨터공학과

● 연구분야 : Analog ICs for biomedical application

● 이메일 : wiejung@dgist.ac.kr

● 홈페이지 : http://ins.dgist.ac.kr

한국과학기술원 바이오및뇌공학과 박사과정 석동열

#### **Session 3 Energy Harvesting**

이번 세션에서는 다양한 환경에서 초저전력 장치를 구동하기 위한 첨단 에너지 하베스팅 기술들이 소개되었다. C3-1에서는 온도 변화에 따라 입력 극성이 바뀌는 열전발전 소자를 위해, 양극성을 지원하며 폭넓은 전압 변환 비율을 제공하는 완전 통합형 하이브리드 SC 전력 변환기를 제안하였다. C3-2는 해양 에너지 환경의 저주파 특성을 고려하여, 다단 바이어스-플립 구조와 액티브 정류기를 결합한 TENG 기반 에너지 하베스터로 최대 77.7%의 효율을 달성하였다. C3-3에서는 다중 RF 소스를 동시에 활용하는 3D MPPT 기반 하베스팅 시스템을 통해 높은 감도와 넓은 입력 전력 범위를 확보하여 IoT 등 무선센서 네트워크에 최적화된 솔루션을 제시했다. 마지막으로 C3-4는 세 가지 에너지원(PZT, PV, TEG)을 동시에 처리하는 TGPR 하베스터를 통해 기존 대비 2,771% 향상된 출력 전력을 보여주며, 다양한 에너지원 통합의 가능성을 입증했다. 이처럼 이번 세션의 연구들은 각각의 특화된 환경에서 에너지 수확의 효율성과 확장성을 극대화하며, 차세대 자율형전자 시스템 구축에 기여할 수 있음을 보여준다.

#C3-1 본 논문은 열전발전기(TEG) 기반의 에너지 하베스팅을 위해 양극성 입력을 지원하고 넓은 전압 변환 비율(VCR)을 처리할 수 있는 완전 통합형 스위치드 캐패시터(SC) 전력 변환기를 제안한다. TEG의 출력 전압은 온도 변화와 방향에 따라 -1V에서 +1V까지 넓게 변동하는데, 기존 SC 기반 변환기는 단극성 입력만 지원해 입력 극성이 바뀌면 동작이 불가능하거나 복잡한 추가 회로가 필요했다. 또한 기존 구조는 VCR 범위가 제한적이어서 효율적인 전력 변환이 어려웠다. 이를 해결하기 위해 본 논문은 Dickson R-SC와 4-레일 CSCR(Continuously Scalable Conversion Ratio)을 결합한 하이브리드 구조를 제안하였다. Dickson R-SC가 생성한 중간 전압(VX)을 통해 CSCR의 전압 스윙을 줄여 충전 손실을 낮추고, CSCR은 연속적이고 부드러운 다단 전압 변환으로 높은 효율을 유지한다. 별도의 스위치 없이도 양극성 입력을 실시간으로 감지해 전환하며, 1kHz 샘플링으로 극성을 판단해 자동으로 최대 전력점을 추적(MPPT)한다.

칩은 180nm BCD 공정으로 제작되었으며, ±130mV의 낮은 입력 전압에서도 동작 가능하다. 출력은 항상 1.2V로 안정화되고, -6.48~+6.67 범위의 VCR에서 75% 이상의 효율을 유지하며, 최대 효율은 84%를 기록했다. 또한 130Ω의 TEG 내부 저항에서 1.31mW, 34Ω에서는 10.8mW의 출력 전력을 달성했다. 완전 CMOS 기반으로 구현되어 소형화에 적합하며, IoT와 웨어러블 등 환경 변화가 심한 자율형 시스템에서 안정적이고 효율적인 전력

[그림 1] 제안된 재구성 가능한 하이브리드 Dickson-CSCR 전력 변환기의 시스템 아키텍처를 보여준다. Dickson R-SC 블록과 4-레일 CSCR 블록으로 구성되며, 두 블록이 결합되어 양극성 입력을 동시에 처리하고 넓은 전압 변환 비율(VCR)을 지원한다. 중간 전압(VX)은 Dickson R-SC에서 생성되어 CSCR의 전압 스윙을 줄이고 충전 손실 감소시킨다. 또한, AC 입력 극성 변화에 실시간으로 대응하며, 단일 칩 내에서 최대 전력지점 추적과 안정적인 전력 출력을 동시에 구현할 수 있다.

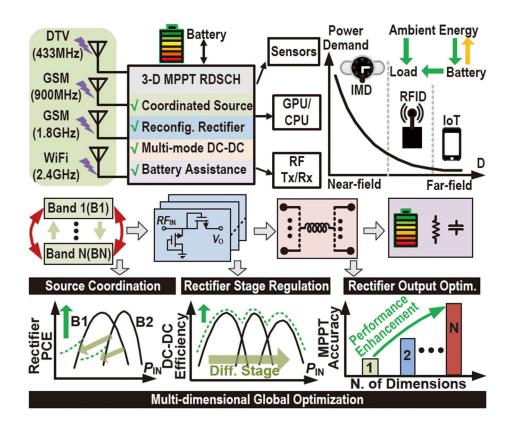

#C3-3 본 논문은 IoT, 웨어러블 기기, 무선 센서 네트워크(WSN) 등 배터리 교체가 어렵거나 불가능한 초저전력 장치를 위해 두 개의 RF 에너지원으로부터 동시에 전력을 수확할 수 있는 차세대 RF 에너지 하베스팅 시스템을 제안한다. 기존 RF 하베스터는 단일 주파수만 처리할 수 있어 특정 밴드에 신호가 없으면 전력 공급이 불가능하며, 여러 RF 소스를 동시에 사용할 경우 간섭으로 인해 효율이 저하되는 문제가 있었다. 또한 고정된 회로 구조와 단순한 MPPT(Maximum Power Point Tracking) 제어로는 입력 전력의 변화에 즉각 대응하기 어려워 안정적인 전력 공급이 힘들었다. 이를 해결하기 위해 제안된 시스템은 세 가지 측면에서 전역 최적화(global optimization)를 수행한다.

첫째, 에너지원 간 조율(Energy Source Coordination Control)을 통해 두 RF 소스가 서로 간섭하지 않으면서 전력을 최대한 효율적으로 결합하도록 관리한다. 둘째, 정류기 출력 최적화(Rectifier Output Optimization)를 통해 입력 신호의 크기와 조건에 따라 정류기의 동작 방식을 실시간으로 조정하여 다양한 입력 상황에서도 최적의 효율을 유지한다. 셋째, 정류기 단계 제어(Rectifier Stage Regulation)를 통해 다단계 DC-DC 컨버터를 활용하여 넓은 입력 전압 범위에서도 일정하고 안정적인 출력 전압을 제공한다.

이를 구현하기 위해 시스템은 재구성 가능한 정류기(Reconfigurable Rectifier)와 다단계 DC-DC 컨버터를 사용하며, 두 RF 입력의 전압·전류·출력을 동시에 고려하는 제어 알고리즘을 적용한다. 그 결과 -24.1 dBm의 매우 낮은 입력 전력에서도 동작이 가능하며, 최대 71%의 전력 변환 효율(PCE)을 달성했다. 실험에서 두 RF 소스를 동시에 사용했을때 단일 소스 대비 더 안정적이고 지속적인 전력 공급이 가능함이 입증되었으며, 이는 스마트 시티 센서, 산업용 모니터링 시스템 등 배터리 없는 자율 전력 공급이 필요한 다양한 응용 분야에서 활용 가능성이 높다.

[그림 2] 제안된 3차원 MPPT 이중 밴드 RF 에너지 하베스터의 개념도

## 저자정보

## 석동열 박사과정 대학원생

● 소속 : 한국과학기술원

● 연구분야 : 바이오메디컬 응용 회로설계(센서 및 신호처리)

• 이메일 : sukd10@kaist.ac.kr

단국대학교 파운드리공학과 석사과정 조혁준

#### **Session 18 Power Management**

Session 18에서는 전력 관리를 주제로 총 5편의 논문이 발표되었다. 발표된 논문들은 각각 RF 시스템을 위한 Supply Modulator, LED Driver, Buck Regulator, AI 프로세서를 위한 전력 관리 시스템 그리고 DLDO를 주제로 각각 한 편씩 발표되었다. 이 논문들은 공통적으로 시스템에 안정적인 전력 및 전압을 공급하기 위한 기술적 과제에 집중한다. 급격한부하 변화 시 발생하는 전압 강하나 리플과 같은 전압 변동 문제를 최소화하고, 각 회로의 특성에 맞춰 전압 안정성을 향상시키는 방향으로 연구가 진행되고 있음을 확인할 수있다. 이러한 흐름 속에서, 저전압·고효율이 중요한 최신 프로세서를 위한 전력 관리 기술이 주목받고 있다. 이에 따라 발표된 논문 중 DLDO 회로 자체에 대한 논문 1편과 AI 프로세서 시스템을 위한 LDO 관리 기술 논문 1편을 더 깊이 있게 살펴보고자 한다.

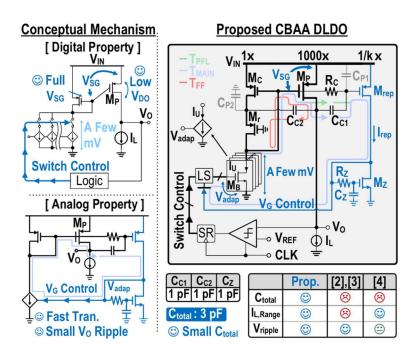

#18-1 본 논문은 서강대학교에서 발표한 논문으로, 최근 SoC의 공급 전압이 점차 낮아 짐에 따라 저전압 환경에서 동작 가능한 LDO의 중요성이 부각되고 있다. 기존 아날로그 LDO는 전압 헤드룸 제약으로 인해 저전압 환경에 적용하기 어렵지만, 디지털 LDO(DLDO)는 낮은 입력 전압에서도 동작이 가능하다는 장점을 갖는다. 그러나 DLDO는 고주파 클럭이나 큰 부하 커패시터가 없을 경우 출력 전압 리플(ripple)과 심각한 언더슛 (undershoot) 문제를 일으키는 한계가 존재한다. 이를 해결하기 위해 논문에서는 전류 미러 기반 아날로그 보조(CBAA) 방식을 적용한 새로운 DLDO 구조를 제안한다. 그림 1 은 제안된 DLDO를 보여준다. 이 방식은 버퍼 트랜지스터 $(M_B)$ 의 수를 디지털 방식으로 제어하며,  $M_B$ 는 딥 트라이오드 영역에서 동작하기 때문에  $V_{DS}$ 가 매우 작은 값만 필요하 다. 이로 인해  $M_p$ 의  $V_{GS}$ 의 제한이 사라져 헤드룸 문제거 해결된다. 또한 고주파 AC 루프 가 과도 상태를 보상하며, 구조적으로 기생 커패시턴스의 낮은 노드에 커플링 커패시터 를 연결하여 전체 커패시턴스를 최소화한다. DC 관점에서 레플리카 회로는 부하 전류에 비례하는 전류를 생성해 제어 전압을 부하 전류에 맞춰 조절한다. 이 과정에서 단위 전 류가 동적으로 변화하여, 기존 구조의 한계였던 작은 부하에서의 리플 문제와 큰 부하에 서의 전류 부족 문제를 동시에 해결한다. AC 관점에서는 출력 전압에 언더슛이 발생하면 커플링 커패시터를 통해  $V_c$ 가 그에 맞춰 떨어지고, 이는 제어 전압 상승으로 출력 전류 가 증가해 보상된다.  $M_z$ ,  $R_z$ ,  $C_z$ 로 구성된 엑티브 제로 $(A_z)$  회로는 과도 상태가 발생했을

때 제어 전압을 증폭시켜 보상 속도를 극대화하는 역할을 한다. 이를 통해 성능 지표에서 0.087fs라는 높은 성능 지수를 달성하며 제안된 구조의 효율성과 안정성을 입증한다.

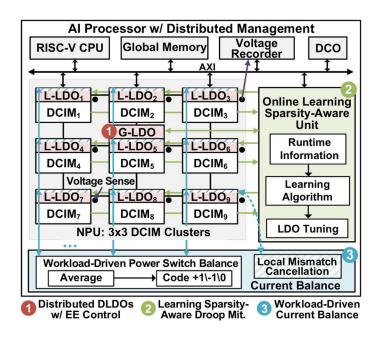

[그림 1] 제안된 CBAA DLDO

#18-2 본 논문은 베이징대학교에서 발표된 논문으로, AI 컴퓨팅의 핵심인 AI 프로세서 및 가속기의 고질적인 전력 관리 문제 해결에 초점을 맞췄다. AI 프로세서는 대규모 병렬 MAC(곱셈-누산) 연산 과정에서 수 암페어(ampere) 수준의 과도 전류가 발생해 전압이 급격히 강하하며, 이는 칩의 안정성을 위협하는 주요 요인으로 작용한다. 또한 실제 AI 모델은 높은 희소성(sparsity)을 가지지만, 희소성이 낮은 상황을 가정해 전압을 공급하기 때문에 불필요한 전력 낭비가 발생한다. 더불어 AI 프로세서는 하나의 LDO가 전체 전력을 담당하는 방식이 아니라 칩 내 여러 구역에 다수의 LDO를 배치하는 구조를 사용한다. 이 경우 LDO 간 작업량이 불균형 하게 분배돼 일부 LDO는 과부하에 걸리고, 나머지는 유휴 상태로 남아 전체 시스템의 전력 전달 효율을 저하시키는 문제가 뒤따른다. 이 같은 문제를 해결하기 위해, 논문은 지능형 분산 전력 관리 시스템을 제안한다. 우선 과도 전류로 인한 전압 강하에 신속히 대응하기 위해 '이중 제어 시스템'을 도입했다. 평상시에는 Global-LDO(G-LDO)가 시스템 전체를 제어하고, 급격한 전압 강하가 발생하면 각구역의 Local-LDO(L-LDO)가 즉시 전압을 복구하는 방식이다. 또한 희소성 문제 해결을위해 연산 희소성과 토글률을 실시간으로 모니터링하고, 이로부터 발생하는 전압 강하데이터를 학습 보상에 활용한다. 그 결과 L-LDO의 기준 전압을 동적으로 최적화해 희소

성에 따른 불필요한 전력 소모를 차단한다. 아울러 분산된 LDO의 부하를 실시간으로 감지하고 전류를 동적으로 재분배해 특정 LDO로의 과부하 집중을 방지, 시스템 전체의 전력 전달 효율을 크게 높였다. 제안된 시스템은 기존 방식 대비 부하가 큰 환경에서 전압 강하를 44.3% 감소시켰으며, 다양한 희소성 조건에서 12.3~22.5%의 성능 향상 또는 21.1~33.3%의 에너지 절감을 달성했다.

[그림 1] 제안된 AI 프로세서 전력 관리 시스템

#### 저자정보

#### 조혁준 석사과정 대학원생

● 소속 : 단국대학교 파운드리공학과

● 연구분야: Biomedical Circuits

• 이메일 : sdi5236@dankook.ac.kr

• 홈페이지: https://sites.google.com/dankook.ac.kr/acs-lab

고려대학교 전기전자공학과 박사과정 이윤호

#### **Session 26 Switching Regulators**

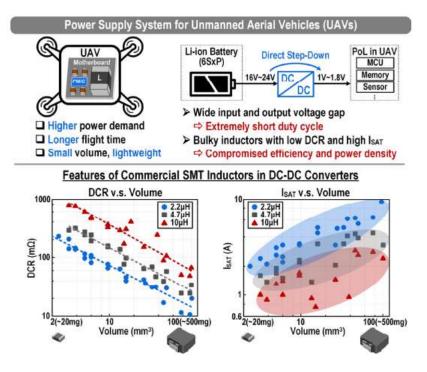

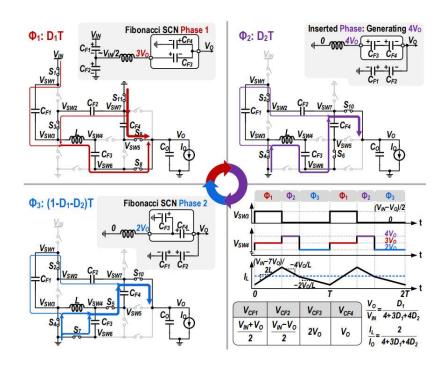

이번 2025 IEEE VLSI의 Session 26은 Switching Regulator를 주제로 총 4편의 논문이 발표되었으며, 가정용 IoT 기기를 위한 AC-DC 컨버터부터 UAV 전원용 하이브리드 컨버터까지 다양한 응용 분야를 다루는 새로운 전력 변환 토폴로지와 효율 향상 기법들이 소개되었다. 이 가운데 본 글에서는 Fibonacci 기반 Switched-Capacitor Network를 활용해 인덕터 전류를 효과적으로 줄이고 전력 밀도와 효율을 동시에 높인 하이브리드 컨버터, 그리고 Unified Imbalance Calibration Technique(UICT)를 적용해 플라잉 커패시터 전압과 인덕터 전류를 동시 밸런싱한 2-페이즈 3-레벨 부스트 컨버터에 초점을 맞추어 살펴보고자한다.

#26-2 본 논문은 6-셀 리튬 이온 배터리를 사용하는 UAV(Unmanned Aerial Vehicle) 시스템을 위해, 높은 전압 변환비에서도 고효율을 달성할 수 있는 1-stage 하이브리드 백 컨버터를 소개하였다. 아래의 그림 1과 같이 모든 부하 전류가 인덕터를 통해 전달되는 기존의 백 컨버터에서는, 높은 전류 구동 능력과 높은 효율을 확보하기 위해 낮은 DCR과높은 포화 전류를 만족하는 큰 부피의 인덕터가 필요하다. 그러나 이러한 인덕터는 전력밀도를 크게 낮추고, 인덕터의 DCR로 인한 전도성 손실을 증가시켜 전체 시스템 효율을저하시키는 주요 원인이 된다. 이를 해결하기 위해 본 논문은 Fibonacci 기반 Switched-Capacitor Network와 3-Phase 동작을 결합하여 인덕터 전류를 Σ-Fibonacci 영역으로 최소화함과 동시에 인덕터 전압 스윙을 줄임으로써, 인덕터의 DCR 및 ACR 손실을 동시에저감하는 고효율 전력 변환 토폴로지를 제안하였다.

[그림 1] Power supply system for UAVs and features of commercial SMT inductors

아래 그림 2는 제안된 Dual-Path 하이브리드 벅 컨버터의 회로와 동작 원리를 보여준다. 제안된 컨버터는 세 개의 위상으로 동작하며, 각 위상마다 플라잉 커패시터와 인덕터를 통해 출력으로 전류를 공급한다. Φ1 구간에서는 인덕터가 VIN/2 전압으로 에너지를 충전하는 동시에, CF1 및 CF2가 직렬로 출력과 연결되어 인덕터와 함께 세 개의 경로로 출력에 전류를 공급한다. Φ2 구간에서는 인덕터가 방전하면서 CF3 및 CF4가 동시에 충전되고, 인덕터 전류 경로와 CF1과 CF2의 전류 경로를 통해 출력에 전류가 전달된다. Φ3 구간에서는 인덕터, CF3, CF2 세 개의 전류 경로로 출력 전류를 공급한다. 이와 같은 3-Phase 동작과 플라잉 커패시터 네트워크 덕분에 출력 전류가 인덕터 하나에 집중되지않고 세 경로 또는 두 경로로 분산된다. 결과적으로 인덕터의 평균 전류가 대폭 줄어들어 인덕터에 의한 DCR 손실이 감소한다. 또한, CF1과 CF2는 항상 직렬로 연결되어 인덕터 양단에 인가되는 전압을 입력 전압의 절반 수준으로 낮춰 주기 때문에, 인덕터 전류 스윙이 크게 줄어들어 인덕터의 AC 손실을 감소시켜준다. 이로 인해, 더 작은 인덕터로 도 동일한 부하 전류를 고효율로 감당할 수 있어 전체 전력 밀도와 효율이 크게 개선된다. 이러한 기술을 통해 제안된 컨버터는 1.187 W/mm³의 전력 밀도와 93.9%의 높은 피크 효율을 달성했으며, 높은 전압 변환 비에서도 우수한 전력 변환 효율을 보여준다.

[그림 2] Operating principle of the proposed hybrid buck converter

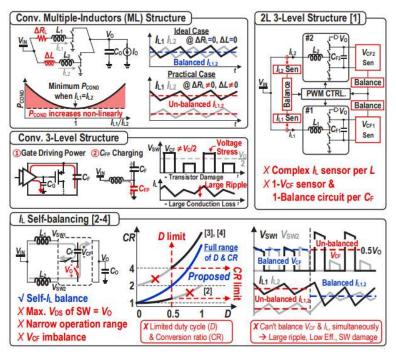

#26-3 본 논문은 LED 드라이버나 배터리 충전기 등 높은 전압이 필요한 모바일 시스템을 위해, 넓은 전압 변환비에서도 안정적으로 동작할 수 있는 2L-3LV 부스트 컨버터를 제안하였다. 아래 그림 3과 같이 기존 다중 인덕터 3-레벨 컨버터는 두 인덕터의 기생저항 및 인덕턴스 등의 불일치로 인한 인덕터 전류 불균형(IL imbalance) 문제와, 플라잉커패시터의 전압 불균형(VCF imbalance) 문제로 인해 출력 전압 리플이 커지고 효율이떨어지며 스위치의 손상 위험까지 초래한다. 특히 기존의 IL self-balancing 기법은 인덕터전류를 맞추는 대신 VCF 불균형이 발생하여 근본적 해결이 어렵고, 동작 가능한 듀티사이클(D) 및 전압 변환비(VCR)가 제한되는 문제가 있었다. 이러한 문제를 해결하기 위해본 논문은 플라잉커패시터를 공유하는 2-L 3-LV 부스트 컨버터 구조와 함께, Unified Imbalance Calibration Technique (UICT)를 제안하였다. UICT는 단일 보정 회로로 플라잉커패시터 전압과 인덕터 전류를 동시에 균형시키며, 동작 범위를 듀티사이클 및 전압 변환비의 제약 없이 확장할 수 있다.

[그림 3] 인덕터 전류 및 플라잉 커패시터 전압 variation과 기존 방식의 한계점

아래 그림 4는 본 논문에서 제안하는 2-L 3-LV 부스트 컨버터와 UICT의 동작 개념을 보여준다. 제안된 회로는 두 개의 인덕터(L1, L2)와 두 개의 플라잉 커패시터(CF1, CF2)가 교차로 연결된 구조로, 한 주기 동안 각 인덕터가 번갈아 가며 CF1과 CF2를 충전 및 방전한다. 이때 L1과 L2의 전류가 불균형해지면 CF1과 CF2의 전압에도 차이가 발생하는데, UICT는 이러한 전압 차이를 감지해 추가적인 보정 전류를 생성한다. UICT는 크게 두 가지 보정 동작으로 이루어진다. 첫째, 공통 모드(CM) 보정은 두 커패시터 전압의 평균값이 출력 전압의 절반(0.5VO)이 되도록 스위칭 기간 ΦC와 ΦD를 조정하여 플라잉 커패시터 전압의 기준점을 맞춘다. 둘째, 차동 모드(DM) 보정은 CF1과 CF2의 전압 차이를 기반으로 두 인덕터의 스위칭 듀티를 서로 다르게 조절해 전류의 평균을 매칭시킨다. 이를통해 인덕터 전류의 차이가 사라지고, CF1과 CF2의 전압도 다시 동일해져 두 경로 모두에서 동일한 전류가 흐르도록 만든다. 결과적으로 제안된 회로는 VCF와 IL을 동시에 균형시키면서도 모든 스위치의 전압 스트레스를 VO/2로 절감시켜, 듀티사이클이나 변환비의 제약 없이 넓은 동작 범위에서 5V 저전압 소자 만으로 안정적인 동작을 할 수 있다.

이러한 기술을 통해 제안된 컨버터는 플라잉 커패시터 전압 오차를 0.92% 미만, 인덕터 전류 밸런싱 오차를 0.22% 미만으로 감소시켜 매우 정밀한 밸런싱을 달성하였다. 또한 듀티사이클이나 변환비 제한 없이 전 영역에서 안정적으로 동작하며, 94.1%의 높은 피크 효율을 보여준다.

#

[그림 4] 본 논문에서 제안한 2-L 3-LV 부스트 컨버터 및 UICT의 동작 개념

## 저자정보

## 이윤호 박사과정 대학원생

● 소속 : 고려대학교

● 연구분야 : Power management ICs

• 이메일 : uknow@korea.ac.kr

• 홈페이지 : https://sites.google.com/site/kubasiclab/home

KAIST 전기및전자공학부 석사과정 박민하

#### Session 33 Wireless Power and Gate Drivers

세션 33은 'Wireless Power and Gate Drivers'를 주제로, 무선 전력 전송의 핵심 과제인 효율 및 전송 거리 개선과 이를 위한 핵심 구동 부품 기술을 다룬다. 이 세션에서는 50미터에 이르는 장거리에서도 전력을 보낼 수 있는 다중 수신 안테나(Multi-Rectenna) 기술이 소개되어 무선 전력 전송의 적용 범위를 크게 확장했다. 또한, 전력 전송과 동시에 데이터를 양방향으로 주고받을 수 있는 전력-데이터 통합 송수신 IC 논문도 발표되어, 전력 전달과 통신을 하나의 시스템으로 통합하는 기술의 중요성을 보여주었다. 또한 시스템의 효율을 극대화하는 부품 연구도 활발히 진행되었다. 특히, GaN 반도체를 구동하는 게이트 드라이버 기술이 주목받았다. 이 기술은 스위치 구동 시 발생하는 에너지를 재활용하고, 음(-)의 전압을 생성하여 시스템의 전력 효율을 극적으로 향상시키는 데 기여한다. 결론적으로 무선 전력 기술이 단순히 충전의 편의성을 넘어, 전송 거리의 한계를 극복하고 다른 기능과 융합하며 시스템의 전반적인 효율을 극대화하는 방향으로 발전하고 있음을 알 수 있다.

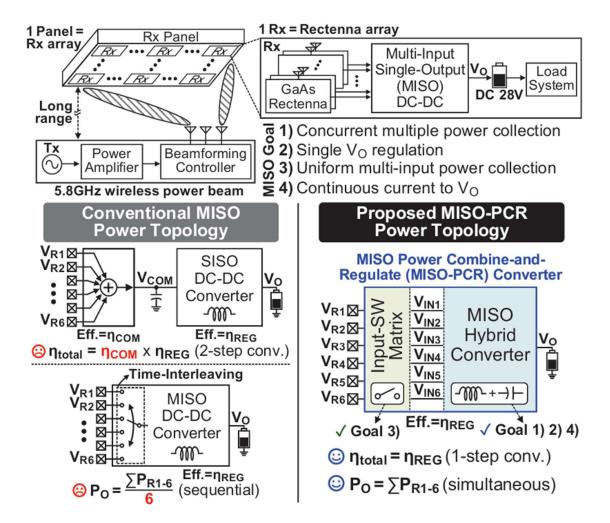

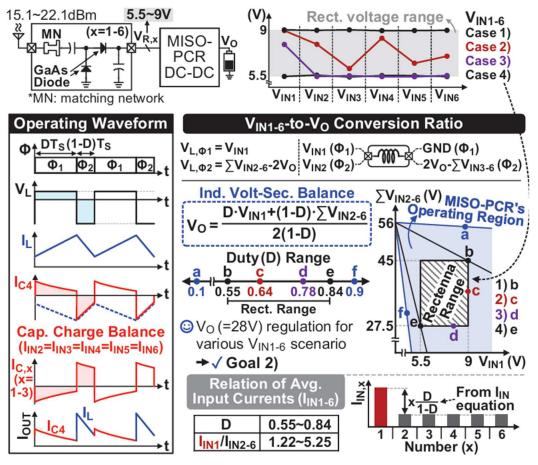

#33-2 이 논문은 한국과학기술원(KAIST)과 한국전기연구원(KERI)의 공동 연구팀이 발표한 것으로, 5.8GHz RF 무선 전력 전송(WPT) 수신기(Rx)를 위한 다중 입력-단일 출력 전력결합 및 조절(MISO-PCR) 부스트 컨버터 칩을 개발하였다. 이 칩은 30개의 GaAs 정류 안테나(rectennas)로부터 수신된 여러 전력을 동시에 수집, 결합하여 단일의 28V로 안정화된 출력으로 변환하는 기능을 수행한다.

장거리 무선 전력 전송은 유망한 기술이지만, 거리가 멀어질수록 수신되는 전력이 급격히 약해지는 문제가 있다. 이를 해결하기 위해 여러 개의 수신 안테나를 배열하고 빔포밍 송신기(Tx) 기술을 이용해 전송 거리를 늘리는 방안이 연구되고 있다. 예를 들어, 효율70%인 정류 안테나 한 개가 20dBm의 전력을 수신할 때, 30개로 구성된 배열은 약 2W의 전력을 전달할 수 있다. 그러나 이 전력을 모두 사용하기 위해서는 모든 안테나의 출력을 동시에 추출하여 단일 버스로 통합해야 한다. 기존의 전력 결합기는 전압을 안정화하는 기능이 없어 별도의 DC-DC 컨버터가 필요했고, 이는 효율 감소로 이어졌다.

[그림 1] RF-WPT 정류 안테나 배열로부터 다중 소스 전력을 수집하기 위한 제안된 MISO-PCR 전력 관리의 개념도

본 논문은 이러한 한계를 극복하기 위해 MISO-PCR 부스트 컨버터를 제안한다. 이 칩은 여러 정류 안테나의 출력을 단일 단계에서 동시에 결합하고 안정화된 전압을 제공한다. 또한, 여러 입력 소스에서 균일하게 전력을 추출할 수 있도록 알고리즘적 입력 스위치 매트릭스와 결합되어 있다.

논문에 제시된 [그림 1]은 이 시스템의 작동 방식을 시각적으로 보여준다. [그림 1]의 상단은 범포밍 송신기가 여러 개의 수신 안테나 배열에 전력을 전송하는 전체 시스템 구성을 나타내며, 이는 장거리 무선 전력 전송을 가능하게 하는 핵심 원리이다. [그림 1]의 왼쪽 하단은 기존 기술의 한계를 보여준다. 기존 방식은 여러 개의 입력 소스를 각각의 DC-DC 컨버터를 거쳐 전압을 조절한 뒤 합치거나, 순차적으로 전력을 수확하는 방식이어서 비효율적이었다. 반면, 오른쪽 하단은 논문에서 제안하는 MISO-PCR 칩을 보여준다. 이 칩은 여러 입력(Multi-Input)을 받아 단일 출력(Single-Output)으로 전력 결합(Power Combine)하고 안정화(Regulate)하는 과정을 한 번에 수행한다.

[그림 2] MISO-PCR 부스트 컨버터의 토폴로지 및 작동

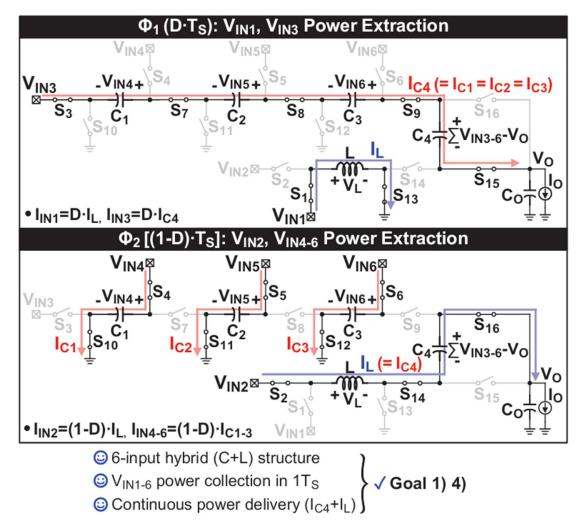

논문에서 제안하는 MISO-PCR 토폴로지는 6개의 DC 입력( $V_{IN1-6}$ ), 4개의 플라이-커패시터  $(C_{1-4})$ , 1개의 인덕터(L), 그리고 1개의 단일 출력( $V_o$ )으로 구성된다. 이 컨버터는 한 스위칭 주기( $V_s$ ) 동안 두 가지 위상( $V_s$ )으로 동작한다.  $V_s$  위상( $V_s$ ) 동안  $V_s$  동안  $V_s$  시이에 지를 공급하고,  $V_s$  의해 미리 충전되었기 때문에, 이제  $V_s$  인결된다. 이전  $V_s$  위상에서  $V_s$  이 가지 충전된다. 이로써  $V_s$  이 되어 미리 충전되었기 때문에, 이제  $V_s$  인 $V_s$  이 위상( $V_s$  이 위성을 통해 매주기마다 모든 입력에서 전력을 동시에 추출하여 최대의 전력 수집을 가능하게 한다.

[그림 3] ISO-PCR의 6개 입력에서  $V_0$ 로의 변환 및 입력 전류.

MISO-PCR 컨버터는 6개의 입력 전압( $V_{IN1-6}$ )을 하나의 출력( $V_o$ )으로 변환하며, 그 변환비율은  $V_o = [D \cdot V_{IN} + (1-D) \cdot \sum V_{IN2-6}]/[2 \cdot (1-D)]$ 로 계산된다. 이 수식은 듀티 비(D)를 제어함으로써 입력 전압이 크게 변하더라도  $V_o$ 를 28V로 안정화시킬 수 있음을 보여준다. 예를 들어, 정류 안테나의 전압이 5.5V에서 9V 사이일 때, 이 컨버터는 0.55에서 0.84 사이의 듀티 비 조절만으로 안정적인 28V 출력을 유지할 수 있다. 그러나 이 회로토폴로지 자체는  $V_{IN1}$ 에서 추출되는 전류( $I_{IN1}$ )가 다른 입력( $I_{IN1-6}$ 과 D/(1-D) 배만큼 차이가 나는 전류 불균형 문제를 가지고 있다.

논문은 이러한 전류 불균형 문제를 해결하기 위해 알고리즘적 입력-스위치 매트릭스를 도입한다. 이 매트릭스는 6개의 정류 안테나 출력 $V_{R1-6}$ )과 MISO-PCR의 입력( $V_{IN1-6}$ ) 사이의 연결을 동적으로 재구성한다. 이 과정을 통해 MISO-PCR 컨버터 내부의 전류 불균형에도 불구하고, 모든 정류 안테나에서 추출되는 평균 전류가 균등하게 유지되도록 보장한다. 이 매트릭스가 없으면 일부 정류 안테나의 전력이 완전히 수확되지 않아 전체효율이 감소하게 된다. 논문은 또한 정류 안테나 전압이 불균일할 때 발생할 수 있는 '하

드-차징(hard-charging)' 손실을 최소화하는 알고리즘을 제안하여, 최악의 경우 손실 횟수를 16회에서 6회로 줄일 수 있음을 밝혔다.

제안된 MISO-PCR 칩은 5V CMOS와 고전압 LDMOS 소자를 사용하여 제작되었다. 특히, 스위치(S15, S16)는 출력( $V_o$ )으로부터의 역류를 막기 위해 백투백(back-to-back) 형태로 구성되었다. 이 칩은 외부 제어 없이도 스스로 동작할 수 있으며, 전원 공급이 없는 상태에서 자동으로 시작하는 콜드-스타트업(cold-startup) 기능과 자율적인 작동을 지원하여 시스템의 독립성을 높였다.

180nm BCD 공정으로 제작된 칩을 20.4 x 19cm² 크기의 RF-WPT 수신기 패널에 통합하여 그 성능을 측정하였고, 5.8GHz 무선 전력 전송 시스템은 4m(실내)와 50m(실외) 거리에서 성공적으로 작동했다. 50m 거리에서 최대 3.1W의 출력 전력을 달성했으며, MISO-PCR 칩 자체는 최고 93.2%의 높은 효율을 기록했다. 전체 수신기 시스템의 효율은 입력 전력이 22.1dBm일 때 최고 63.8%에 도달했다. 결론적으로, 이 연구는 제안된 MISO-PCR 시스템이 기존 연구들에 비해 더 나은 성능을 보였음을 증명했다.

### 저자정보

### 박민하 석사과정 대학원생

● 소속 : KAIST

● 연구분야 : 디지털 회로 설계● 이메일 : mhpark@ics.kaist.ac.kr

● 홈페이지: https://idec.or.k

KAIST 전기및전자공학부 석사과정 박민하

### **Session 29 Communication and Processors**

세션 29는 'Communication and Processors'라는 주제로, 미래 통신 기술과 이를 지원하는 핵심 프로세서 연구들을 다루고 있다. 이 세션에서는 대규모 다중 사용자 MIMO(Massive MU-MIMO) 시스템의 데이터 처리 효율을 극대화하는 검출기(detector), 고속 광통신을 위한 에너지 효율적인 FEC(Forward Error Correction) 디코더, 그리고 디지털 신호 처리 (DSP)에 특화된 고성능 RISC-V 벡터 프로세서 등 다양한 하드웨어 기술들이 발표되었다. 특히, AI 시대에 맞춰 전력 효율을 극대화한 NPU(Neural Processing Unit) 논문도 포함되어, 통신 기술의 발전과 더불어 이를 처리하는 프로세서 기술의 중요성을 보여주고 있다.

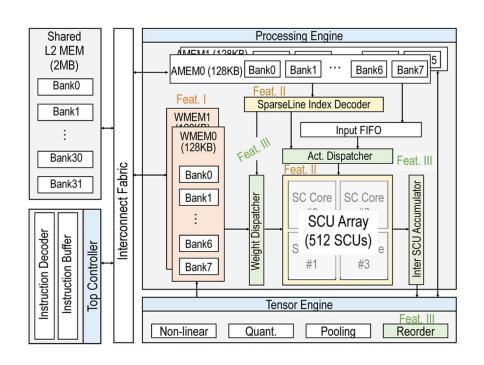

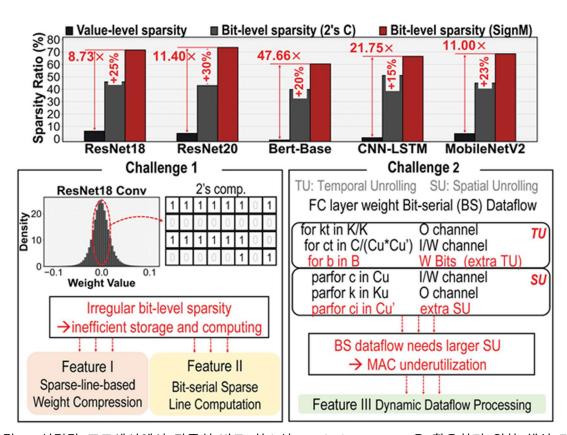

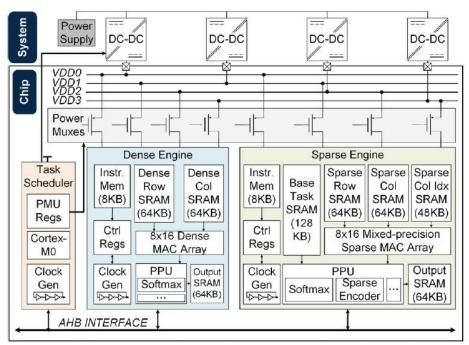

#29-4 KU Leuven과 NXP Semiconductor가 공동 발표한 이 논문은 훈련 없이도 높은 에 너지 효율을 달성하는 신경망 처리 장치(NPU)를 다루고 있다. 이 칩은 신경망 및 트랜스 포머 워크로드에서 공격적인 가중치 압축과 높은 연산 활용도를 동시에 달성하기 위해 구조화된 비트 단위 희소성(structured bit-level sparsity)과 동적 데이터 흐름(dynamic dataflows)을 활용하는 희소 신경망 프로세서이다.

[그림 1] 테스트 칩의 아키텍처 (3가지 특징)

위의 그림은 논문이 제안하는 NPU(Neural Processing Unit)의 전체적인 하드웨어 아키텍처를 보여준다. 단순한 블록 다이어그램을 넘어, 논문의 핵심적인 세 가지 기술적 특징인훈련 없는 비트 단위 희소성(training-free structured bit-level sparsity), 동적 데이터 흐름 (dynamic dataflows), 그리고 이를 통합하는 명령어 기반의 프로세서(instruction-programmable processor)가 어떻게 유기적으로 연결되어 있는지를 알 수 있다. 특히, 데이터가 메모리(L2, L1)에서 나와 동적 디스패처를 거쳐 512개의 SCU(Sparse Line Computation Unit) 배열로 전달되는 흐름을 보여줌으로써, 효율적인 데이터 이동과 연산이 이 칩의 핵심임을 알 수 있다.

이 논문은 AI 하드웨어 설계의 두 가지 핵심 난제를 해결하려는 시도로 볼 수 있다. 첫째, AI 모델의 비대화에 따른 연산량 및 메모리 요구량 증가, 둘째, 이를 효율적으로 처리해야 하는 전력 효율성 문제이다. 특히, 모바일 및 엣지 디바이스와 같이 전력 제약이 심한 환경에서는 이 두 가지 과제를 동시에 해결하는 것이 필수적이다. 저자들은 이 문제를 해결하기 위해 가중치의 비트 단위 희소성이라는 새로운 관점에 주목했다.

[그림 2] 신경망 프로세서에서 가중치-비트 희소성(weight-bit sparsity)을 활용하기 위한 핵심 과제

전통적인 신경망 희소화(sparsity) 기법은 주로 가중치의 '값(value)'이 0에 가까운 것을 제거하는 방식이었으며, 전통적인 신경망 희소화(sparsity) 기법은 주로 가중치의 '값'이 0에 가까운 것을 제거하는 방식으로, 이는 모델의 크기를 줄이는 효과가 있었다. 그러나 이를 위해서는 모델을 희소성에 맞게 re-training해야 하는 복잡한 과정을 거쳐야 했다.

이 논문은 이러한 한계를 극복하기 위해 비트 단위 희소성(Bit-level Sparsity, BLS)이라는 혁신적인 접근법을 제안한다. 즉, BLS는 가중치를 이진수로 표현했을 때, '0' 비트가 많은 현상을 이용하는 것이다. 특히 Sign-Magnitude(SignM) 인코딩을 사용하면 '0' 비트가 더 많이 생성되는데, 이 논문은 이 '0' 비트가 있는 연산을 건너뛰는 방식으로 하드웨어 효율을 극대화한다.

첫 번째는 메모리 효율적 비트라인 압축 기술이다. 메모리 효율적 비트라인 압축: 가중치를 여러 그룹으로 묶고, 각 그룹 내에서 동일한 유효성을 가진 비트 라인을 식별한다. 이중 '0' 비트로만 이루어진 라인(Zero-lines)은 제거하고, 비제로 라인(Non-Zero-Lines, NZLs)만 인코딩하여 저장한다. 이를 통해 메모리 사용량을 획기적으로 줄일 수 있다.

두 번째는 Zero-bit Line Boost (ZLBoost) 기술이다. 이는 가중치의 '0' 비트 위치를 유연하게 조절하는 기술로, 기존의 양자화 방법들이 비제로 비트가 연속적으로 위치해야 한다는 제약을 가졌던 것과 달리, 손실이 있는 SignM 인코딩을 통해 더 높은 압축률을 달성한다. 예를 들어, BERT-Base 모델에서 ZLBoost는 0.5% 미만의 정확도 손실로 2.47배의 가중치 압축을 달성했다. 이는 기존 4-bit 양자화 기법(PTQ)이 약 10%의 정확도 손실을 보였던 것과 비교해 압도적인 성능이다. 이 기술은 재훈련 없이도 높은 압축률과 정확도를 동시에 보장함으로써, AI 모델 경량화의 새로운 가능성을 열었다.

|                            | DA-SignM     | USCA          | HUAA          | Onyx         | This                      |

|----------------------------|--------------|---------------|---------------|--------------|---------------------------|

|                            | ISSCC'23 [2] | ISSCC'23 [12] | ISSCC'23 [13] | VLSI'24 [14] | work                      |

| Technology                 | 28nm         | 28nm          | 28nm          | 12nm         | 16nm                      |

| Area [mm <sup>2</sup> ]    | 7.75         | 2.69          | 7.81          | 23           | 6.5                       |

| Frequency [MHz]            | 55-285       | 60-400        | 100-500       | 500-980      | 50-280                    |

| Voltage [V]                | 0.65-0.9     | 0.48-0.92     | 0.66-1.3      | 0.6-1.0      | 0.565-0.93                |

| Number of MACs             | 1024         | 256           | 1024          | 1536         | 512                       |

| On-Chip Mem. [KB]          | 1074         | 176           | 1120          | 4500         | 2560                      |

| Sparsity Support           | W bit        | A value       | None          | W/A value    | W bit                     |

| Flexible Dataflow          | None         | None          | Yes           | None         | Yes                       |

| Power [mW]                 | 6.6-179.4    | 366           | 17-174        | -            | 6.13-102.4                |

| Peak Performance           | 27.97@0.9V   | _             | -             | 73.09        | 54.72@0.93V*2             |

| [BTOPS] <sup>*1</sup>      | 5.38@0.65V   | _             |               |              | 11.66@0.6V <sup>-3</sup>  |

| Effective Peak             | -            | 99.2@0.85V    | 480-716.8     | -            | 190.71@0.93V*4            |

| EE [E-BTOPS/W]*1           |              | 264.9@0.48V   |               |              | 645.12@0.6V <sup>*5</sup> |

| Sparse Peak                | 268.8@0.9V   | 179.2@0.85V   | _             | 193.5@0.66V, | 550.4@0.93V*2             |

| EE [S-BTOPS/W]*1           | 517.7@0.65V  | 767.3@0.48V   | _             | 500MHz *6    | 1320.8@0.6V*3             |

| Area Efficiency            | 3.61@0.9V    | -             | -             | 1.59         | 8.41@0.93V*2              |

| [BTOPS/mm <sup>2</sup> ]*1 | 0.69@0.65V   |               |               |              | 1.79@0.6V <sup>*3</sup>   |

<sup>\*1:</sup> One operation (OP) is one mult. or one add. \*2: Measured at the highest performance point. 0.93V for logic, 0.92V for mem., 280MHz, 6 sparse lines. Activation with 50% sparsity.

### [그림 3] 최신 기술 비교 표

이 표는 논문에서 제안하는 NPU의 성능이 기존의 최신 기술과 비교했을 때 어느 정도수준인지 객관적으로 보여주는 자료이다. 공정 기술, 칩 면적, 연산 능력, 전력 소모, 그리고 에너지 효율과 같은 핵심 지표들을 다른 주요 NPU들과 비교하였다. 특히 S-BTOPS/W(Sparse BTOPS/W)라는 희소 연산 효율 지표에서 압도적인 우위를 보여주며, 논문이 주장하는 비트 단위 희소성 기술이 기존의 어떤 기술보다도 효과적임을 입증한다.

희소성 기술을 적용하면 연산량이 불규칙해지므로, 하드웨어 연산기의 활용도를 유지하기 어렵다는 문제가 발생한다. 이 논문은 이를 해결하기 위해 동적 데이터 흐름을 적용한다. 512개의 SCU(Sparse Line Computation Unit)로 구성된 연산 배열은 특정 작업에 고정된 데이터 흐름을 사용하는 것이 아니라, 현재 처리하는 레이어의 특성(차원)에 맞춰최적의 데이터 이동 경로를 선택한다.

이 논문은 단순히 AI 하드웨어의 성능을 개선하는 것을 넘어, 새로운 설계 패러다임을 제시했다는 점에서 매우 중요한 의미를 가진다. '훈련 없이 비트 단위 희소성을 활용'하는 방식은 기존의 희소화 연구와 차별화되는 고유한 아이디어이며, 이는 하드웨어 설계 단계에서 효율을 극대화하면서도 소프트웨어적인 복잡성(재훈련)을 제거하여, 실제 상용화에 유리한 이점을 제공한다.

<sup>\*3:</sup> Measured at the highest efficiency point 0.6V for logic, 0.55V for mem., 71.4MHz, 6 ZLs.

<sup>\*4 \*5:</sup> Peak EE excluding skipped sparse computations w/o ZLBoost. \*6: Reported TOPS/W was not clearly declared to E-BTOPS/W or S-BTOPS/W, used as S-BTOPS/W as sparsity is exploited.

또한 550~1320 BTOPS/W라는 높은 에너지 효율은 모바일, 엣지 컴퓨팅, 사물 인터넷 (IoT) 등 전력 제약이 심한 환경에서 AI를 구동하는 데 필수적인 성능이다. 이 칩의 효율은 기존 최고 기술 대비 최대 6.82배나 높아, 차세대 AI 가속기 시장에서 강력한 경쟁력을 가질 수 있음을 시사한다.

그리고, CNN, RNN, 트랜스포머 등 다양한 AI 모델을 효과적으로 처리할 수 있는 동적 데이터 흐름 지원은 이 칩이 특정 애플리케이션에 국한되지 않고 광범위하게 활용될 수 있음을 보여준다. 이는 현재의 AI 기술이 특정 모델에 의존하기보다 다양한 모델이 공존하는 방향으로 나아가고 있다는 점을 고려할 때 매우 중요한 특징이다.

종합적으로 볼 때, 훈련 없는 희소성, 동적 데이터 흐름과 같은 혁신적인 아이디어를 성공적으로 구현함으로써, AI 하드웨어 연구의 새로운 방향을 제시하고 고성능-고효율 AI 시스템 개발에 기여를 하였다.

### 저자정보

### 박민하 석사과정 대학원생

● 소속 : KAIST

● 연구분야 : 디지털 회로 설계● 이메일 : mhpark@ics.kaist.ac.kr● 홈페이지 : https://idec.or.k

고려대학교 전기전자공학과 박사과정 이윤호

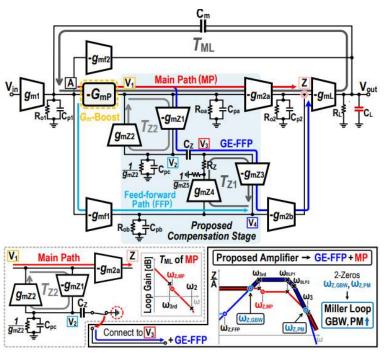

## **Session 14 Analog Techniques**

이번 2025 IEEE VLSI Session 14는 Analog 및 Mixed-Signal 회로를 주제로 총 4편의 논문이 발표되었으며, mm-Wave PLL을 위한 초고속 TDC, 저전압 동작이 가능한 SAR ADC, 대용량 load capacitor(CL)를 구동할 수 있는 3-Stage 고이득 증폭기, 그리고 고효율 배터리 구동 Class-D 오디오 앰프까지 다양한 응용 분야에서 회로 안정성과 선형성 및 전력효율을 개선하는 새로운 회로 기법들이 소개되었다. 이 가운데 본 글에서는 Gm-Boosting과 Gain-Enhancing Feedforward Path(GE-FFP)를 활용해 대용량 CL에서도 안정적으로 동작하는 3-Stage 앰프, 그리고 True-Zero-Switching(TZS) 기법을 통해 무부하 시스위칭 손실과 대기 전류를 획기적으로 줄이고 2VBAT까지 출력 전압을 부스트할 수 있는 배터리 구동 Class-D 오디오 앰프에 초점을 맞추어 살펴보고자 한다.

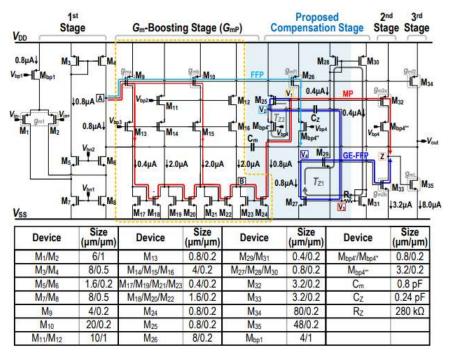

#14-3 본 논문은 대용량 커패시터를 구동해야 하는 전력 관리 및 아날로그 프런트엔드 시스템을 위해, 높은 DC 이득과 넓은 대역폭을 확보하면서 안정적으로 동작할 수 있는 3-Stage 앰프를 제안하였다. 기존 3-Stage 앰프는 큰 CL에 의해 첫 번째 극점(ω1st)이 낮아지고 Miller 루프(TML)의 중간 주파수 이득이 감소하여, 영점과 극점의 분리가 충분히 확보되지 못해 위상 여유(PM)가 줄고 불안정해지는 문제가 있다. 이를 해결하기 위해본 논문은 아래 그림 5와 같이 Gm-Boosting Cell(GmP)과 Gain-Enhancing Feedforward Path(GE-FFP)를 결합한 새로운 보상 구조를 제안하였다. 제안된 구조에서 메인 경로만 사용할 경우 기존 Active Zero 보상 앰프와 동일하게 동작하지만, GE-FFP가 추가되면 고주파에서 GE-FFP의 이득이 메인 경로보다 커져 TML의 GBW을 크게 확장시킨다. 또한 두개의 로컬 피드백 루프(TZ1, TZ2)가 상호 연관되어 Adaptive Passive Zero(A-PZ)를 형성하기 때문에, PVT 변화에도 안정적으로 위상 여유를 확보할 수 있다. 이로써 대용량 CL 구동 시에도 넓은 GBW와 충분한 PM을 동시에 달성할 수 있다.

[그림 5] 본 논문에서 제안한 Gm-boosted Amplifier의 구조

아래 그림 6과 같이 GmP는 Nested Current Mirror(NCM) 구조를 통해 38 dB의 높은 이득을 제공하면서도 고주파 극점은 GBW보다 높게 유지해 보상 복잡도를 늘리지 않는다. GE-FFP는 메인 경로(Main Path)와 병렬로 추가된 신호 경로로, 주파수가 높아질수록이득이 증가하는 특성을 이용해 TML의 GBW와 PM을 동시에 개선한다. 특히 커패시터 CZ를 접지 대신 노드 V3에 연결하여, 동일한 소자로 메인 경로의 영점(ωZ,MP)을 생성함과 동시에 GE-FFP를 형성하도록 구현하여 추가적인 소자 오버헤드를 최소화하였다. 이러한 기술들을 통해 제안된 앰프는 130 dB이상의 DC 이득과 160nF의 CL에서 1.47 MHz GBW 및 51°의 PM을 달성하며, 기존 대비 FOMS 16.9배, LC-FOMS 30.6배 향상된 성능을보여준다.

[그림 6] 본 논문에서 제안한 Gm-boosted Amplifier의 회로도

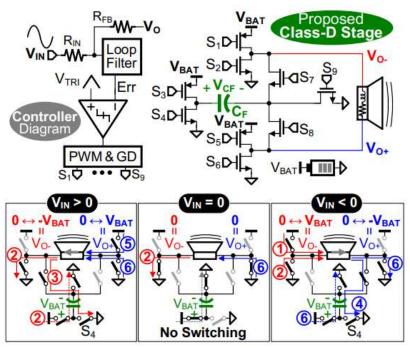

#14-4 본 논문은 배터리로 구동되는 기기에서 출력 전력(POUT)을 배터리 전압(VBAT)의 2배까지 부스트 하면서도 낮은 대기 전류(IQ)와 높은 오디오 성능을 달성하기 위해 새로운 단일단(1-stage) 부스트 Class-D 오디오 앰프를 제안하였다. 기존 Class-D 앰프는 PWM 스위칭이 입력이 0일 때도 지속되어 IQ가 커지고, 부스트 컨버터를 별도로 사용하여 2단 전력 변환에 따른 효율 저하와 추가 LC 필터가 필요하며, -VBAT 생성 방식을 적용하는 방식에선 모드 전환 시 출력에 왜곡이 발생하는 문제들이 있었다. 이를 해결하기위해 본 논문은 아래 그림 7과 같이 단일 플라잉 커패시터(CF) 기반의 부스트 토폴로지와 True-Zero-Switching(TZS) 기법을 결합한 새로운 Class-D 앰프를 제안하였다. 해당 구조는 VIN이 0보다 클 시, CF를 VBAT으로 충전한 뒤 플립하여 -VBAT을 출력에 인가하고,반대로 VIN이 0보다 작을 시, 반대 위상으로 동작시켜 fully-differential 출력(VO+&VO-)이 ±VBAT 범위를 갖도록 만든다. 이를 통해 외부 부스트 컨버터 없이도 2VBAT의 출력전압 스윙을 얻어 최대 4배의 출력 전력을 제공할 수 있다. 또한 TZS를 적용한 변조 방식은 VIN=0일 때 VO+와 VO-를 0V로 유지해 불필요한 스위칭을 억제한다.

[그림 7] 본 논문에서 제안한 Class-D Amplifier의 회로도 및 동작

그러나 아래 그림 8과 같이 앰프 컨트롤러의 메인 루프만으로는 에러 신호(ErrP, ErrN) 가 VCM에서 서서히 드리프트해 데드타임 임계값을 넘을 시, 스위칭이 발생하고 오디오 출력에 스파이크가 생겨 불필요한 IQ 증가와 노이즈가 발생한다. 이를 방지하기 위해 제안된 TZS 보조 루프는 두 에러 신호의 차(|ErrP - ErrN|)가 PWM 검출 한계(VTH,PWM)를 초과하면 빠른 보정 펄스를 루프 필터에 공급하여 Err을 VCM으로 되돌리고, 출력 스테이지는 정적으로 접지된 상태로 유지해 스위칭 없이 IQ를 0으로 만든다. 결과적으로, 제안된 오디오 앰프는 VBAT=5V에서 ±10V 차동 출력 스윙을 제공하고, VIN=0에서 IQ를 기존 3.2mA에서 910μA로 감소시켰으며, 92.6% 피크 효율 및 3.56 W 최대 출력 전력과 -81.6 dB THD+N, 122.8 dB SNR을 달성하였다.

[그림 8] 본 논문에서 제안한 True-Zero-Switching(TZS) 루프의 동작 파형

## 저자정보

### 이윤호 박사과정 대학원생

● 소속 : 고려대학교

● 연구분야: Power management ICs

• 이메일 : uknow@korea.ac.kr

• 홈페이지: https://sites.google.com/site/kubasiclab/home

고려대학교 전기및전자공학부 박사과정 안재웅

### **Session 6 Imagers**

이번 2025 VLSI의 Session 6에서는 Imagers라는 주제로 총 4편의 논문이 발표되었다. 이중 #6-1은 global shutter CIS에 관련된 내용을 제안하였으며, #6-3은 센서 내부에 CNN을 넣은 이미지 센서에 관련된 내용이다. 또한 #6-4는 ADAS에 사용되는 이미지 센서에 관련된 내용이다.

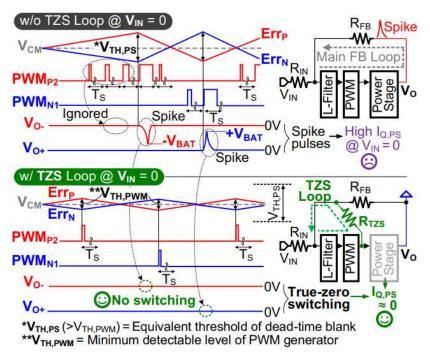

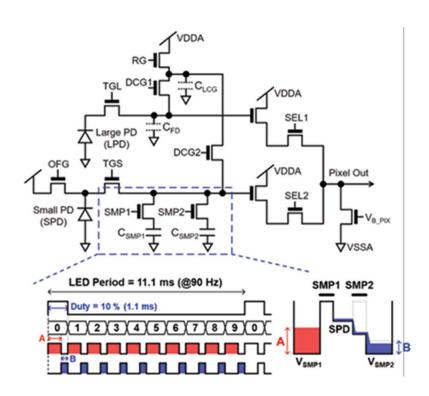

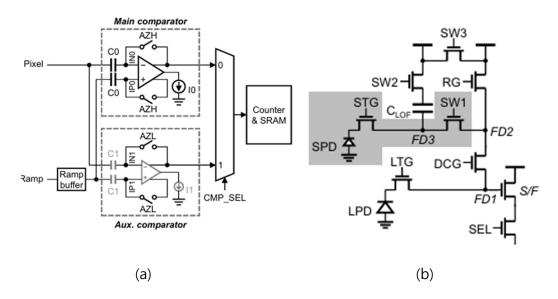

#6-1 논문은 CMOS image sensor (CIS) 기존의 rolling shutter CIS가 빠르게 움직이는 물체 포착에 어려움이 생겨 이를 해결하기 위해 나온 global shutter CIS에 관한 내용이다. 제안된 digital pixel sensor (DPS)는 포토다이오드를 두 개로 나눈 구조로, large photodiode (LPD)는 저조도 환경에서 SNR을 확보하는 데 쓰이고, small PD (SPD)는 high dynamic range (HDR) 구간에서 포화 없이 계조를 유지하는 데 쓰인다. 이때 SPD에는 chopping operation을 추가해 LED flicker 및 저주파 성분을 줄여 주며, 결과적으로 HDR 에서도 유효 동작 범위를 넓힌다. 또한 single-slope ADC에 두 개의 DC coupling capacitor를 더해 auto-zero operation이 가능하도록 구성하여 random noise와 fixed pattern noise (FPN) 문제를 동시에 낮췄다. 픽셀/컬럼 경로에서 생기는 오프셋과 저주파 잡음을 한 번 더 상쇄해 주는 셈이라, global shutter 동작 시 프레임 전역의 균일도에도 도움이 된다. 이러한 기법들을 통해 analog gain 16에서 1.22 e-rms의 낮은 노이즈를 달성했고, 3 MP GS 모드 60 fps에서 전력 소모는 270 mW 수준이다. 또한 기존 논문들과 비교했을 때 픽셀 크기, random noise, HDR, 전력 소모 측면에서 경쟁력 있는 수치를 보였고, 빠른 피사체에서도 왜곡을 줄이면서 저조도·고조도 환경 모두에서 신호 품질을 유지했다.

[그림 2] #6-1에서 제시한 split PD를 사용하고, chopping operation을 사용한 pixel structure

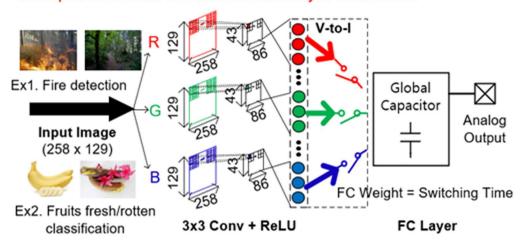

#6-3 논문은 edge device에서 늘어나는 vision task에 대응하기 위해, AI processor가 센서 밖에 따로 있는 구조 대신 센서 내부에 CNN을 넣은 이미지 센서에 관한 내용이다. 기존 연구들은 전력 소모가 크거나, 복잡한 작업에서 정확도가 떨어지거나, weight 정밀도가 낮아서 한계가 있었다. 이 논문은 258×129 pixel array를 3×3 sub-pixel array (SPA) 단위로 묶고, exposure time을 weight로 programmable하게 조절한다. Conv layer의 fractional weight는 -8~+8 범위를 0.1 step으로 구현하는데, SPA 내부 픽셀들의 exposure 시작 시 점과 up/down 카운트 반복 횟수를 조합하는 two-step Conv로 실현한다. 이렇게 얻은 feature map (FM)은 ReLU를 거친 뒤 analog MAC에서 전류로 변환되고, 5-bit fullyconnected (FC) weights가 스위치 on 시간을 정해 global capacitor에 전하를 누적한다. 픽 셀은 nMOS-only PWM pixel 구조를 써서 fill factor를 30.6% 향상시켰고, 컬럼 공유 pMOS로 면적/배선도 줄였다. RGB 채널은 독립적으로 처리해서 색 채널 감도의 차이를 high-resolution fractional weights로 학습 단계에서 보정한다. 본 논문은 채널당 20 fps에 서 137.5 μW를 소모했고, iFoM 206.6 pJ/pixel·frame을 달성했다. digital MAC 대비 analog MAC은 면적 83%, 에너지 68.8% 절감이 보고된다. 벤치 태스크에서는 fire detection 89.6%, fruits freshness 90.9%의 정확도를 보였고, 동일한 FM 수에서 gray scale 대비 RGB 사용 시 성능이 17.5% / 31.9% 개선되었다.

### Multispectral Sensor with Embedded 2-Layer CNN Model

### 4 Key Features of Proposed Vision Sensor

- ① Multispectral Sensor ③ High-resolution Weights ④ Analog FC Layer

- ② nMOS-only PWM Pixel 5b FC weights

- Improved fill factor

Enabling RGB compensation

[그림 3] 제안한 multispectral vision sensor의 구조와 중요 내용

#6-4 논문은 advanced driver assistance system (ADAS)에 많이 사용되는 이미지 센서와 관련된 논문이다. High dynamic range (HDR)와 light-emitting diode flicker mitigation (LFM)은 자동차 센서에서 가장 중요한 요소다. 본 논문의 픽셀은 large photodiode (LPD)와 small photodiode (SPD)로 구성되어 있고, 단일 노출(single exposure)에서 포토다이오드 조합에 따라 총 네 번의 센싱을 수행한다. 이미지 센서는 12-bit single-slope ADC를 사용하며, 네 번에 걸쳐 얻은 결과는 28-bit HDR merger에서 결합되어 최대 144 dB 수준의 HDR을 표현하고 최대 16× analog gain을 지원한다. 일반적으로 면적을 줄이기 위해 두 개의 comparator가 하나의 load를 공유하기도 하지만, 이 경우 noise coupling 문제가 생길 수 있어 본 논문은 auxiliary comparator를 도입했다. 또한 ADC ramp slope와 잡음은 oversampling으로 평균화되며, readout 시간 제약을 고려해 모드별로 ADC 분해능과 oversampling 비를 재구성한다(예: LPD-H 10-bit OS4 등). 이러한 기법들을 통해 analog gain 16×, OS4에서, OS가 없을 때 대비 SNR1을 39% 낮출 수 있었다. read noise는 room temperature에서 0.5 e-, Tj 85°C에서 0.55 e-를 달성했다. 다른 논문들과 비교했을 때도 제안 기법은 우수한 FoM과 경쟁력 있는 HDR 및 SNR을 보였다.

[그림 3] (a) 제안하는 comparator 구조와 (b) 제안하는 sub-pixel 구조

## 저자정보

## 안재웅 박사과정 대학원생

● 소속 : 고려대학교

● 연구분야 : 디스플레이 드라이버 / 픽셀 보상 / 터치 센서

• 이메일 : ajw1104@korea.ac.kr

• 홈페이지 : https://sites.google.com/site/kubasiclab/home

고려대학교 전기전자공학과 박사과정 이윤호

### Session 27 Sensing and Ranging Technologies

이번 2025 VLSI의 Session 27은 sensing and ranging technologies와 관련된 총 4편의 논문이 발표되었으며, 이들 논문에서는 SPAD 기반 이미지 센서, LiDAR를 위한 SPAD direct ToF 센서, 그리고 초소형 금속저항 기반 온도 센서 등 다양한 센싱 기술이 소개되었다. 그 중에서도 가중치 기반 포톤 계수와 연속 이벤트 검출기를 결합해 단일 촬영으로 156 dB 초고역 동작범위와 LED 플리커 억제를 구현한 2.1Mpixel SPAD 이미지 센서, 그리고 등가시간 샘플링과 온 칩 에코 추출로 데이터를 대폭 축소하면서 25M points/s를 달성한 SPAD Direct ToF LiDAR 센서에 초점을 맞추어 살펴보고자 한다.

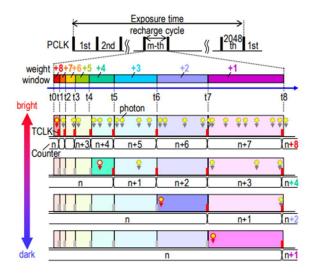

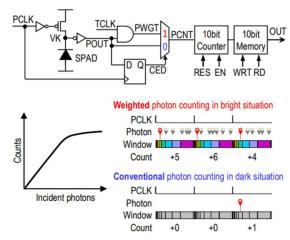

#27-1 본 논문은 자동차 환경에서 요구되는 차세대 이미지 센서의 한계를 극복하고자, 2/3-inch 2.1Mpixel 해상도의 3D 적층 SPAD 이미지 센서를 제안하였다. 자율주행 및 운전자 보조 시스템 (ADAS) 환경에서는 초저조도와 고휘도의 상황이 동시에 존재할 수 있으며, 이때 기존 CMOS 이미지 센서 (CIS)는 LED 플리커에 취약하고 넓은 동작범위 (HDR)을 위해 다중 노출 방식을 사용하므로 SNR 불균형과 색 재현 문제가 발생하는 한계가 있었다. 이러한 문제를 해결하기 위해, 본 연구에서는 weighted photon counting (WPC) 기법을 도입하여 단일 촬영(single-shot)으로 156dB의 초고역 동작범위를 확보하고, 동시에 LED 플리커 억제 기능을 구현하였다.

아래 그림 9는 WPC 동작 원리를 설명하는 그림이다. 한 프레임을 다수의 충전 주기로 나눈 뒤, 첫 번째 광자가 도착하는 시간에 따라 가중치(1~8)를 부여하여 누적 계수하는 방식이다. 이로써 밝은 장면에서는 포화되지 않고, 어두운 장면에서도 충분한 신호를 확보해 단일 촬영에서 156dB HDR을 구현한다. 그러나 저조도 환경에서는 포톤이 드물게 도착한다. 이때는 아래 그림 10과 같이 consecutive event detector (CED)가 WPC를 자동으로 비활성화하여 일반 포톤 카운팅으로 전환, 저조도에서의 SNR 저하를 방지한다.

[그림 9] Weighted photon counting (WPC) operation principle

[그림 10] Pixel circuit diagram and conceptual view of consecutive event detector

제안된 센서는 픽셀 단위 글로벌 셔터와 intra-frame nondestructive 판독을 지원해, 짧은 노출 (1ms)과 긴 노출 (25ms)을 동시에 획득함으로써 모션 블러 최소화와 저조도 성능 확보를 동시에 달성한다. 실험 결과, 0.1 lux 환경에서 최대 120m 거리 보행자 인식이가능했고, 130Hz LED 점멸 환경에서도 플리커 억제가 검증되었다. 따라서 본 연구는 WPC+CDE 기반 단일 촬영 HDR과 플리커 억제라는 새로운 접근을 제시하여, 자율주행및 ADAS 환경에서 기존 CIS 기반 센서를 대체할 수 있는 가능성을 보여준다.

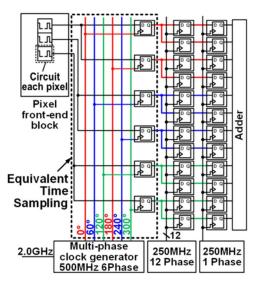

#27-2 본 논문은 장거리이면서 시야가 넓은 자동차용 light detection and ranging (LiDAR) 요구를 만족시키기 위해, 후면 조사 (BSI) 방식의 SPAD 픽셀을 사용한 Direct Time-of-Flight (Direct ToF) 심도 센서를 제안한다. 기존 LiDAR는 낮은 포인트 레이트 와 샘플링

속도를 높이면 데이터가 과도하게 늘어나는 문제가 있었는데, 본 연구는 센서 내부에 등가 3 GHz 수준의 시간 해상도를 제공하는 equivalent time sampling (ETS)와, 센서 안에서 즉시 데이터를 줄여 주는 파이프라인을 결합해 이 문제를 해결했다. 아래 그림 11은 multi-phase 사용시 ETS의 다이어그램을 보여주고 있다. 500 MHz에서 여섯 개의 위상을 사용해 같은 신호를 서로 다른 순간에 샘플링하고, 이렇게 얻은 결과를 조합하여 3 GHz에 해당하는 세밀한 시간 분해능을 만든다. 이후 내부 동작 부담을 낮추기 위해 250 MHz에서 열두개의 위상을 거쳐 하나의 위상으로 재정렬한다.

[그림 11] Equivalent time sampling circuit diagram using multi-phase clocks

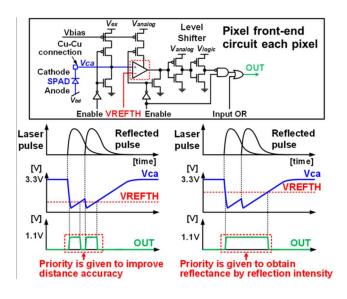

아래 그림 12는 픽셀 아래에 배치된 차동 비교기와 임계값 조절 기능을 보여 준다. SPAD의 cathode를 비교기에 직접 연결해 신호를 뽑아 내고, 임계값을 조절하여 상황에 따라 거리 정확도를 우선할지, 아니면 반사 강도 정보를 우선할지 선택할 수 있도록 했다.

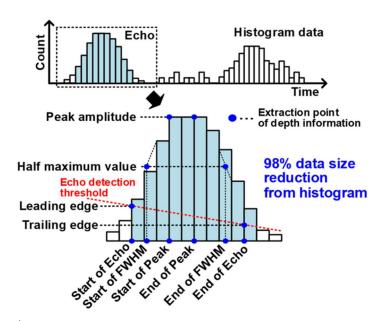

또한 1×3 수직 SPAD를 매크로 픽셀로 묶어(위상 샘플 합산) SRAM 히스토그램에 누적한다. 아래 그림 13은 전용 에코 처리 회로가 히스토그램에서 반사파의 피크와 시간 정보를 골라 내어 깊이만 출력하기 때문에, 원래의 히스토그램과 비교하면 약 98 퍼센트까지 데이터가 줄어드는 것을 보여준다. 파이프라인 제어는 약 19.6 μs 간격의 슬롯으로동작하여, 샘플링·저장·추출·출력이 동시에 진행되며, 그 결과 초당 20프레임에서 초당 2천5백만 포인트의 출력을 구현했다.

[그림 13] Depth extraction from echo histograms and timestamps

칩은 2-Die Stacked 구조(상단 BSI SPAD 어레이, 하단 신호처리 IC)로 제작되었고, SPAD 픽셀은 10 μm 피치 105×1572 배열로 구성된다. 유효 매크로픽셀 520개를 통해 수평 120°·수직 0.05°의 분해능을 지원하며, 20 fps에서 초당 25 M pts/s의 3D 포인트 클라우드를 생성한다. 실험 결과, 반사율 10%와 일조 120 klux 조건에서 300 m까지 탐지 가능하고, 250 m 거리의 높이 25 cm 물체도 분해해 냈다. 따라서 본 센서는 자율주행 차량의 안정적 원거리 감지에 최적화된 차세대 LiDAR 솔루션으로 평가된다.

# 저자정보

## 이윤호 박사과정 대학원생

● 소속 : 고려대학교

● 연구분야 : Power management ICs

• 이메일 : uknow@korea.ac.kr

● 홈페이지: https://sites.google.com/site/kubasiclab/home

고려대학교 전기및전자공학부 박사과정 안재웅

### **Session 20 Acoustic Sensors**

이번 2025 VLSI의 Session 20에서는 acoustic sensors라는 주제로 총 5편의 논문이 발표되었다. 이 중 #20-1은 shunt-resistor-based current sensing에 관한 내용이며, #20-2은 internal acoustic activity detection에 관한 내용이다. 마지막으로 #20-3은 스마트 회의실환경에서의 automatic speaker tracking을 다룬다.

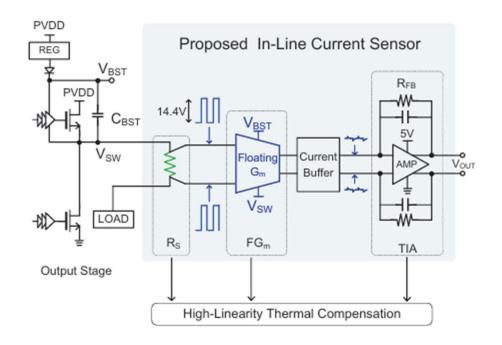

#20-1 High-linearity shunt-resistor-based current sensing은 스피커의 비이상성을 보정하기 위해 사용된다. 다만 shunt resistor의 발열 때문에 on-chip만으로는 선형도가 깨지기쉽고, 그래서 off-chip 저항이나 특수 공정 저항을 쓰면 비용·부피가 커진다. 또 Class-D의 PWM 스위칭이 전압 글리치와 왜곡을 유발하므로 이 역시 해결해야 한다. 본 논문은 shunt resistor가 부하 전류를 전압으로 변환하고, 이를 Floating Gm (FGm)으로 다시 전류로 바꾼 뒤, current buffer를 거쳐 TIA로 보내 최종 출력 전압을 만드는 구조를 제안한다. Shunt resistor는 diffusion 저항으로 구현하고, depletion 효과를 줄이기 위해 complementary body connection을 썼다. 또한 shunt의 self-heating으로 FGm 내부 저항과의 온도·선형 매칭이 틀어지는 문제에 대해, FGm 저항을 여러 sub-unit으로 분산 배치해열 매칭을 잡았다. 측정 결과, HD3는 2 A@1 kHz에서 20 dB 감소했고, DR은 89.1 dB(A-weighted)를 달성했다. THD+N은 최고 -87.2 dB까지 개선되었으며, 기존 대비 1 kHz와 6 kHz에서 각각 17.1 dB/28.2 dB 더 낮았다. PWM 공통모드 억제는 14.4 V 스윙에서 최대 2 MHz까지 가능해 기존 125 kHz 대비 16배 확장되었고, 전류 범위는 ±6 A를 지원한다.

[그림 2] #20-1에서 제시한 전체 시스템

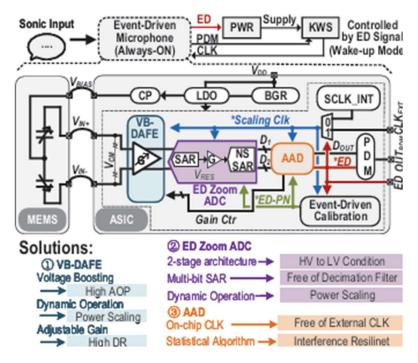

#20-2 Multi-modal AI가 microphone 입력으로 각광받고 있다. 이를 쓰기 위해서는 always-on acoustic activity detection (AAD)가 컨트롤을 하는데, 이때 지속적인 전력 소모와 외부 clock 의존이 문제다. 본 논문은 voltage-boosting dynamic analog front end (VB-DAFE)를 사용해 신호를 boosting하고 gain을 프로그래머블하게 만든다. VB-DAFE는 reservoir capacitor와 load capacitor의 비(CB/CL)를 조절해 voltage gain을 설정한다. 이출력은 zoom-ADC로 들어가며, 1단에서는 CDAC가 coarse 변환을 수행하고, 남은 전압은 2단의 noise-shaping SAR ADC(NS-SAR)가 처리해서 AAD 판단에 필요한 multi-bit 데이터를 만든다. 제안한 AAD 알고리즘은 입력 신호·노이즈·간섭의 time-domain 통계를 이용해 detection threshold를 자동 조정함으로써 false trigger를 줄인다. 측정 결과, 1.8 V에서 131 dBSPL AOP(THD+N 10%, 1 kHz), 66.3 dB-A SNR, 103.3 dB DR를 달성했고, self-clocked AAD로 외부 clock 없이 standby 105.7 μA(@128 kHz 내부 clock)를 구현했다.

[그림 2] #20-2에서 제시한 전체 시스템

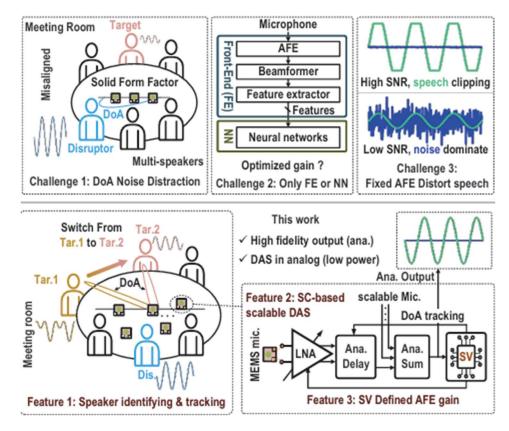

#20-3 논문은 smart meeting room에서 말하는 사람의 목소리를 추적하고 interferences를 제거하는 automatic speaker tracking에 관한 것이다. 기존의 power detector (PD)—based direction of arrival (DoA)나 AFE gain control은 노이즈와 disruptor voice에 취약하다. 본 논문은 speaker verification (SV)와 CNN을 결합하여 disruptor-voice noise 환경에서도 동작 가능하도록 했다. 이때 delay-and-sum (DAS) 빔포머가 채널들의 delay를 정렬·합산해 isolated voice를 생성하는데, high-bit-width DFF 대신 capacitors를 사용하여 power와 area를 크게 줄였다. 또한 SV 모듈은 4-layer CNN으로 time domain에서 52-dimensional embedded speech feature를 추출하며, 첫 번째 layer는 analog-based로 구성해 feature-extraction power를 1.48× 줄였다. 아울러 SV-score-based optimization 알고리즘이 AFE gain을 조절해 SNR을 높여, input SNR이 낮아도 output SNR을 +1.4 dB 개선했다. 측정 결과 SNR은 2.7 dB에서 9.1 dB로 향상되었고, system-level power는 5.2 µW로 낮았다. 또한 기존 논문들과 비교했을 때 약 500× 낮은 power로 동급 성능을 보였다.

[그림 3] 기존의 tracking system의 문제점과 제안하는 기술들.

### 저자정보

### 안재웅 박사과정 대학원생

● 소속 : 고려대학교

● 연구분야 : 디스플레이 드라이버 / 픽셀 보상 / 터치 센서

• 이메일 : ajw1104@korea.ac.kr

• 홈페이지: https://sites.google.com/site/kubasiclab/home

고려대학교 전기및전자공학부 박사과정 안재웅

### **Session 31 MEMS and Display**

이번 2025 VLSI의 Session 31에서는 MEMS and Dipslay 라는 주제로 총 5편의 논문이 발표되었다. 이 중 #31-1은 switched-capacitor MEMS driver를 제안하였고, #31-3는 디스플레이 아래에서 빛을 센싱하는 회로이며 마지막으로 #31-4는 디스플레이 노이즈 저감을 위하 터치 센서를 발표 하였다.

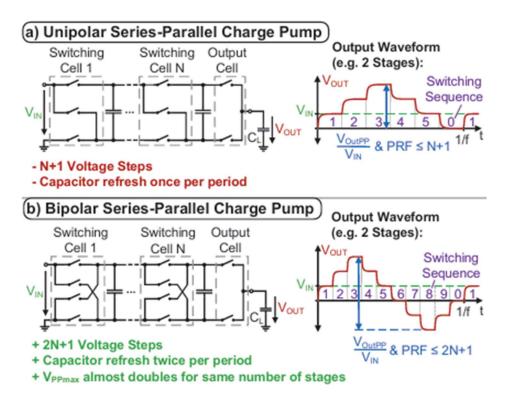

#31-1 논문은 Piezoelectric Micromachined Ultrasonic Transducer(PMUT)와 같은 초음파 MEMS의 용량성 부하를 효율적으로 구동하기 위한 드라이버를 제안한다. PMUT는 본질적으로 커패시터성(load capacitance)이라 충·방전 과정에서 손실이 발생하기 쉽다. 이를 줄이기 위해 저자는 기존 단극성(unipolar) series-parallel charge pump(SP-CP)의 한계를 보완한 양극성(bipolar) SP-CP를 도입한다. 핵심 아이디어는 각 스테이지의 flying capacitor를 한 주기 내에서 병렬→직렬→병렬→반대 극성 직렬로 재구성하여, 동일 스테이지 수에서 양·음 단일단(±) 출력을 모두 생성하고 전하를 회수(recycling)한다. 그 결과한 주기 내 전압 스텝 수가 N+1(단극성)에서 2N+1(양극성)로 늘어나고, 이에 따라 power reduction factor(PRF)의 상한이 사실상 두 배로 확장된다. 실험 결과에서는 동일한 active stage 수로 비교하면, 제안한 양극성 구조는 VCR이 약 84%, PRF가 약 93% 증가했다. 또한 같은 개수의 전압 스텝을 기준으로 보면 VCR은 약 6%, PRF는 약 12% 향상되었다. 구조적 측면에서도 이점이 있다. 같은 스텝 수를 만들 때 단극성 대비 절반의 스테이지만으로 목표 VPP에 도달할 수 있어, 필요한 flying capacitor 수가 줄고 면적·손실을함께 낮출 수 있다.

[그림 1] #31-1에서 제시한 Bipolar SP-CP와 기존의 Unipolar SP-CP

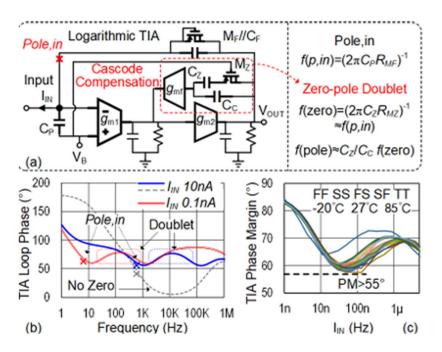

#31-3 논문은 디스플레이 아래에 두는 ambient light sensor(ALS)에 관한 내용이다. 최신스마트폰은 자동 밝기 조절을 위해 ALS를 화면 아래에 배치한다. 하지만 sub-pA까지 측정해야 하고, 짧은 시간 안에 센싱이 돼야 한다. sub-pA 측정을 위해서는 in-band 노이즈뿐 아니라 고주파 대역 노이즈도 처리해야 한다. 보통은 이를 위해 charge amp의 전력을 높이지만, 이 논문은 대신 LPF를 배치해 작은 전력으로도 노이즈를 효과적으로 처리했다. 또한 피드백 다이오드에는 큰 기생 커패시터가 존재해 안정도가 떨어지고 센싱 시간이 느려질 수 있다. 이를 해결하기 위해 2-stage 앰프에 auto-tracking zero 보상기를 적용해, 온도나 공정 코너와 무관하게 위상여유 55도 이상을 유지했다. 이러한 기술을통해 FoM-DR 206.3 dB, DR 146 dB, 0.36 pAPP의 분해능을 달성했다. 기존 논문과 비교해 pA-레벨의 전류 센싱 민감도가 높고, 노이즈·read-out 시간·전력 효율에서도 큰 기생 커패시터 환경에서 가장 좋은 결과를 보였다.

[그림 2] (a) 제안하는 auto-tracking zero frequency compensation (b) loop phase response (c) input amplitude, process, corner에 따른 phase margin.

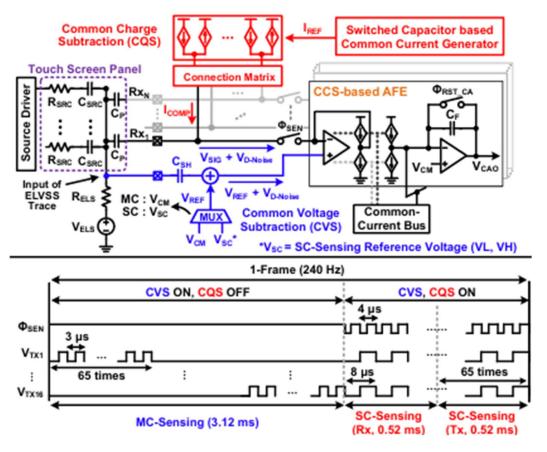

#31-4 논문은 flexible on-cell touch OLED 디스플레이에 쓰이는 터치 센서 IC를 다룬다. 디스플레이의 발달로 기생 커패시턴스가 커지면서, 구동 시 발생하는 디스플레이 노이즈가 터치 센싱에 더 크게 영향을 준다. 이를 해결하기 위해 ELVSS 흔들림을 AC 커플링기반의 differential sensing으로 제거하는 기법을 제안한다. 이 방식은 기존 RGN과 달리고주파 노이즈까지 억제할 수 있다. 또한 self-capacitance sensing에서 기존 BCC와 달리 pre-charging을 이용해 여러 단계로 기생 커패시턴스를 순차 충전·보상하여 동적 범위 (dynamic range)를 확장했다. 그 결과, dynamic range를 500 mV에서 1 V로 확대하고 SNR을 6 dB 개선했다. 더불어 AC 커플링 방식 적용으로 mutual-capacitance와 self-capacitance 모드에서 SNR이 각각 6.33 dB, 6.72 dB 개선되었다. 이러한 기법을 통해 기존 연구 대비 더 큰 기생 커패시턴스를 구동할 수 있으며, 디스플레이 노이즈에 견고한 터치 센서 IC를 구현했다.

[그림 3] #31-4 논문에서 제안한 터치 센서 IC 구조

### 저자정보

## 안재웅 박사과정 대학원생

● 소속 : 고려대학교

● 연구분야 : 디스플레이 드라이버 / 픽셀 보상 / 터치 센서

• 이메일 : ajw1104@korea.ac.kr

• 홈페이지 : https://sites.google.com/site/kubasiclab/home

한국과학기술원 석사과정 윤지원

### **Session 16 Hardware Security**

이번 2025 IEEE VLSI의 Session 16은 Hardware Security라는 주제로 총 4편의 논문이 발표되었다. 이는 반도체 칩과 시스템 설계 단계에서 발생할 수 있는 보안 위협에 대응하기 위한 회로 아키텍처 수준의 기술들을 다루는 분야이며, 이 섹션은 칩 설계와 보안을 융합한 연구를 통해 신뢰성있고 안전한 하드웨어 구현을 목표로 했다.

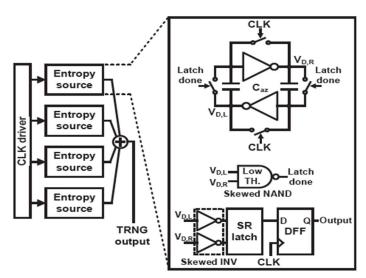

#16-2 본 논문에서는 보정(calibration) 과정 없이도 안정적으로 동작하는 래치 기반 TRNG (Tolerant Latch-Based True Random Number Generator) 를 제안한다. 제안된 회로는 두 인버터와 두 커패시터로 이루어진 직렬 커패시터 연결 cross-coupled latch 구조를 활용하여 auto-zero 단계에서 불일치를 체계적으로 상쇄하고, 이후 잡음만을 증폭함으로써 출력 결정이 본질적인 잡음에 의존하도록 설계되었다. 특히 기존 shunt 방식의 auto zeroing 에서 발생하는 기생 커패시턴스에 대한 offset 샘플링 오류를 근본적으로 제거하는 series-based auto zeroing 기법을 도입하여, 보정 회로 없이도 높은 난수 품질을 확보하였다. 또한 네 개의 셀을 병렬로 결합하여 편향 확률을 효과적으로 줄이고, 설계 복잡도를 완화함으로써, 초미세 공정 환경에서도 소형 저전력 동작과 함께 높은 보안 강도와실용성을 동시에 달성하였다.

Fig. 2. Proposed TRNG system with multiple entropy sources

[그림 1] 다중 엔트로피 소스를 이용한 제안된 TRNG 시스템

실험 결과, 제안된 TRNG는 4nm FinFET 공정에서 제작되어 PVT 코너와 공급 전압, 온도 변동, 그리고 최대 200mV의 전원 노이즈가 주입된 조건에서도 안정적으로 동작하였다. 0.75V에서 1.7pJ/bit의 우수한 에너지 효율을 달성했으며, 최소 엔트로피는 전 주파수 범위에서 0.99 이상을 유지하였다. 또한 NIST SP 800-22와 SP 800-90B 검증에서 각각 97.9% 이상의 통과율과 안정적인 엔트로피 특성을 보여, 추가적인 보정 없이도 최신 설계 대비 동등하거나 더 우수한 난수 품질을 입증하였다. 이를 통해 제안된 TRNG는 초소형, 저전력 환경에서도 높은 신뢰성과 보안성을 제공할 수 있음을 확인하였다.

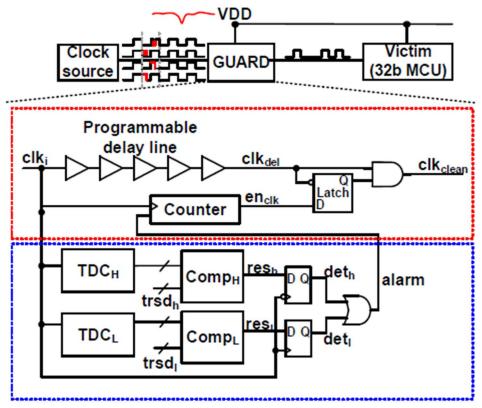

#16-3 본 논문은 클록 및 전압 글리치를 이용한 오류 주입 공격이 하드웨어 보안에 심각한 위협이 됨을 지적하며, 기존 DLL, FLL 기반 탐지 회로들이 보호 기능의 부재, 정상전원 노이즈와의 구분 불가, 실제 공격 검증 부족, 높은 내부 클록 요구 등 한계를 지닌다고 설명한다. 이에 대응하여 저자들은 GUARD 라는 새로운 탐지기를 제안하는데, 이는최적화된 TDC (Time-to-Digital Converter)를 이용해 클록 펄스 이상을 감지하고, 전압글리치로 인한 지연 변화를 탐지하며, 탐지 즉시 클록 게이팅을 통해 피해 프로세서의오류 발생을 방지하는 on-demand 보호 기능을 제공한다. GUARD는 공정, 전압, 온도 변동에도 강인하며 단일 및 다중 글리치 공격을 모두 차단할 수 있는 실용적인 하드웨어보안 솔루션임을 강조한다.

[그림 2] GUARD의 블록 다이어그램 (하단의 파란색은 탐지기, 상단의 빨간색은 보호기로 구분됨)

본 논문에서 제안하는 GUARD 는 탐지기와 보호기로 구성된 구조로, 탐지기는 두 개의 TDC 와 비교 모듈을 통해 클록의 high/low 펄스 폭을 모니터링하여 이상 시 알람을 발생시키고, 보호기는 클록 지연선, ICG, 카운터를 활용해 공격이 탐지되면 즉시 클록을 게이팅하고 안정적인 신호가 회복될 때까지 대기함으로써 피해 MCU 의 오류 발생을 차단한다. 특히 TDC 회로를 최적화하여 100ps 간격의 빠른 펄스도 감지 가능하며, 탐지직후 내부 노드를 빠르게 초기화해 즉시 재사용할 수 있도록 설계되었고, 비트 수준산술 회로를 적용해 임계 경로 지연을 절반으로 줄여 고주파 클록 환경을 지원한다. 또한 테스트 칩에 32bit RISC MCU 와 on-chip 글리치 발생기를 포함해 실제 공격시나리오를 재현, 특정 명령어를 건너뛰어 보안 검사를 회피하는 공격 모델에서도효과적으로 대응함을 입증하였다.

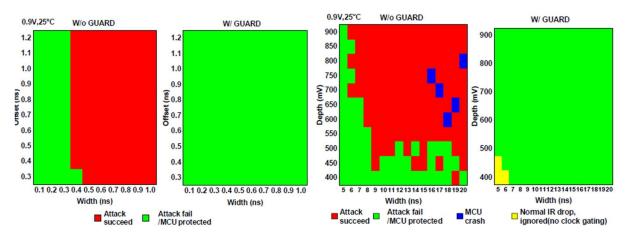

[그림 3] GUARD의 보호 성능 측정 결과: (왼쪽) Clock glitch 공격, (오른쪽) Voltage glitch 공격

Measurement 결과, 28nm CMOS 로 제작된 GUARD 테스트 칩은 실제 글리치 공격실험에서 클록 및 전압 글리치 모두에 대해 100% 방어 성공률을 달성하였으며, 정상적인 동적 IR drop 과 공격을 구분하여 불필요한 보호 동작을 방지할 수 있음을 입증하였다. 또한 -40~125 ℃의 넓은 온도 범위에서도 안정적으로 동작하였고, 기존연구들과 비교해 최초로 탐지와 보호를 동시에 제공하며, 희생 프로세서를 포함한 실제공격 실험을 통해 그 효과성을 검증한 점에서 차별성을 가진다.

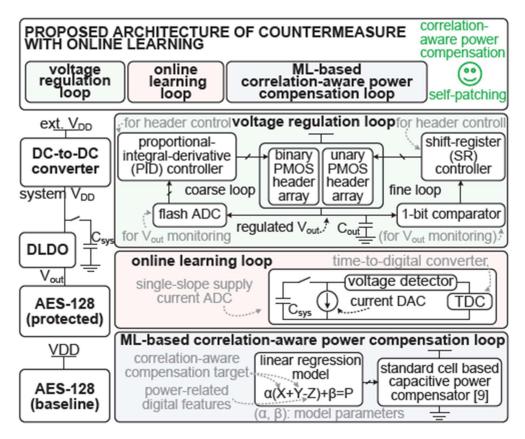

#16-4 본 논문은 전력 분석 사이드 채널 공격 (SCA)에 대응하기 위한 새로운 접근으로, on-chip online 학습 기반 대응책을 최초로 제안한다. 기존의 WDDL, 마스킹, 비동기 회로, 레귤레이터 기반 기법 등은 공정 편차로 인한 칩별 특성과 시간에 따른 노화 현상에 적응하지 못해 보안성이 점차 저하되는 한계를 지닌다. 저자들은 이를 해결하기 위해 칩내부에서 전력 파형을 디지털화하고, 이를 기반으로 전력 보상 머신 러닝 모델을 지속적

으로 학습시켜 mismatch 와 aging 효과를 보장하는 자율 보안 관리 방식을 구현하였다. AES-128 코어 실험을 통해 이 방법이 노화로 인한 18,000배 보안 열화를 완전히 상쇄하고, 최신 최고 수준의 공격 내성(MTD)을 달성함을 입증하여, 장기적으로 안정적이고 칩 맞춤형 보안을 제공할 수 있음을 보여준다.

[그림 4] 전력 분석 공격에 대한 제안된 온라인 학습 기반 대응 기법: 디지털 LDO 기반 전력 디지털와 및 ML기반 전력 보상

이 논문은 AES 코어를 보호하기 위해 전류 측정-온라인 학습-전력 보상으로 이어지는 아키텍처를 제안한다. 전력 공급은 DC-DC와 DLDO 기반 루프가 담당하며, AES 전류는 단일 슬로프 current ADC와 TDC를 통해 디지털화된다. 이후 온라인 학습 루프가 활성화되면, 정보 민감 사이클에서 AES를 Csys로부터 구동하고 방전 시간을 측정해 평균 전류를 얻은 뒤, 이를 선형 회귀 기반 ML모델에 학습시켜 칩별 불일치와 PVT 변동, aging 효과를 보정한다. 학습된 가중치는 전력 보상 루프에 적용되어 AES 연산 feature와 실제 전력 간 상관관계를 무작위화하는 에너지 마스킹으로 이어지며, 이를 통해 추가 회로 부담 없이 장기간 안정적이고 칩 맞춤형 보안을 달성한다.

실험 결과, 제안된 온라인 학습 기반 대응책은 40nm AES 테스트 칩에서 MTD 18만배, TLVA 106만배 향상으로 최고 18억 트레이스 수준의 공격 내성을 달성하였으며, 기존 노이즈 주입 대비 전력 오버헤드는 5배 낮았다. 또한 가속 노화 실험에서 온라인 학습이 없으면 MTD가 10만으로 급락했지만, on-chip 학습을 통해 단 한 번의 학습만으로도 보안성이 완전히 회복되었고, 반복 재학습이 필요 없었다. 더 나아가 모델 학습 속도가 공격자의 off-chip 학습 보다 훨씬 빨라, 1초 미만

의 사전 학습으로도 장기적이고 칩 맞춤형 보안을 제공할 수 있음을 입증하였다.

[그림 5] 보호되지 않은 AES (왼쪽) 과 제안된 on-line 학습 기반 보호 AES (오른쪽) 의 전력 분석 공격 내성 비교

## 저자정보

## 윤지원 석사과정 대학원생

● 소속 : 한국과학기술원 (KAIST)

● 연구분야 : 디지털 회로 설계

● 이메일 : jwyoon@ics.kaist.ac.kr

● 홈페이지: https://ics.kaist.ac.kr

포항공과대학교 반도체대학원 박사과정 박은빈

#### Session 17 CIM-based AI Accelerators

이번 VLSI 2025의 Session C17 CIM-based AI Accelerators는 인메모리 컴퓨팅이 단순한 행렬 곱셈 가속을 넘어 AI 전반과 복잡한 문제 해결까지 영역을 넓혀가고 있음을 보여주었다. 특히 이번 세션의 공통된 흐름은 세 가지로 요약된다. 첫째, DRAM·ReRAM·SRAM 등다양한 메모리 기술을 혼합 활용해 CIM의 한계를 보완하고 에너지 효율을 끌어올리는시도가 활발했다. 둘째, Transformer와 LLM과 같은 최신 AI 워크로드에 특화된 아키텍처가 다수 제시되며, 기존 CNN 중심의 설계를 넘어 실질적인 응용지향 최적화를 강조했다. 셋째, AI 가속을 넘어 SAT와 같은 NP-hard 문제 해결로 응용 범위를 확장하는 연구도 등장해, CIM이 범용 연산 가속기에서 특수 목적 연산 플랫폼으로 진화하고 있음을 보여주었다. 종합적으로 이번 세션은 메모리-연산 융합 구조가 단순한 효율 개선을 넘어, 초저전력·실시간·범용성을 동시에 추구하는 차세대 AI 및 최적화 컴퓨팅의 핵심 축으로 자리잡아가는 흐름을 잘 드러냈다.

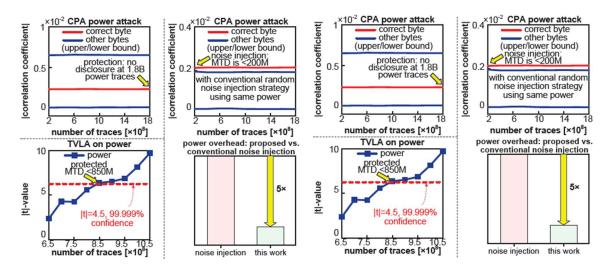

#C17-1은 KAIST와 삼성전자 연구진이 발표한 DIAL (DRAM In-memory Accelerator with LUT and Twisted ADC)로, DRAM 기반 CIM에서 발생하는 LUT와 ADC의 비효율을 동시에 해결한 점이 큰 특징이다. 기존 DRAM CIM은 고정밀 연산을 지원할 때 LUT에 불필요한 0이 다수 포함되어 면적과 전력이 낭비되고, ADC가 병목이 되어 에너지 효율이 급격히 떨어지는 문제가 있었다.

[그림 1] 제안한 DIAL의 전반적인 구조 및 CLUT의 동작 설명과 측정결과

이를 해결하기 위해 DIAL은 Compact LUT (CLUT) 구조를 도입해 불필요한 확장 0을 제거하여 LUT 면적과 전력을 각각 53%, 45% 절감하였고, Twisted Differential ADC (TwiD-ADC)를 설계해 비교기 공유 방식으로 ADC 면적과 전력을 줄이는 동시에 SNDR을 크게 개선하였다. 또한 Dual-Mode Sense Amplifier(DMSA)를 도입해 데이터 패턴에 따라 동작 모드를 전환함으로써 LUT 전력 소모를 추가로 줄였다. 28nm 공정에서 구현된 칩은 GPT-2, VIT 등 고난도 AI 모델에서도 동작이 검증되었으며, 최대 55.4 TFLOPS/W의 에너지 효율을 달성해 기존 DRAM CIM 대비 4.1배 개선된 성능을 보여주었다. 이 논문은 DRAM 기반 CIM이 단순한 이미지 처리 수준을 넘어 LLM과 Transformer와 같은 대규모 AI 모델까지 커버할 수 있는 실질적 확장 가능성을 제시했다는 점에서 의의가 크다.

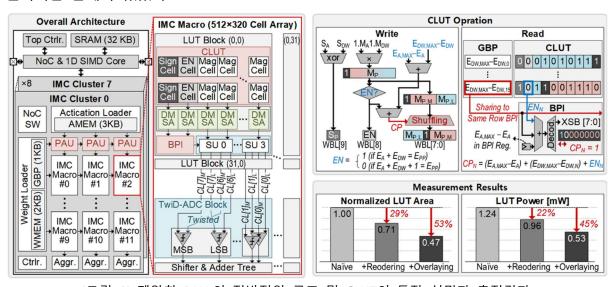

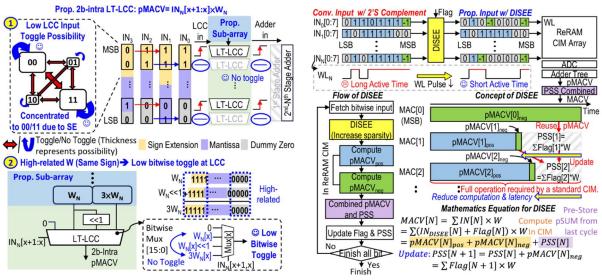

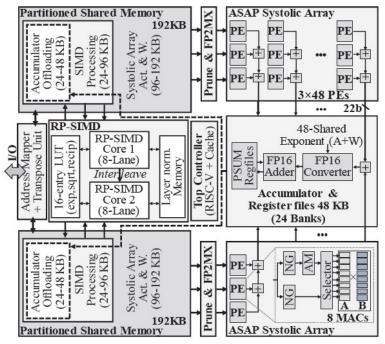

#C17-2는 국립칭화대학교와 TSMC가 공동으로 발표한 22nm Hybrid ReRAM-SRAM CIM 기반 AI-edge Processor로, Transformer와 CNN을 동시에 지원하는 비휘발성 CIM 아키텍처를 제안한 것이 특징이다. 기존 nvCIM은 CNN 가속에는 효과적이지만, Transformer에서는 QKV 연산과 Softmax 같은 동적 가중치 기반 연산 때문에 에너지 효율이 크게 저하되는 문제가 있었다. 이를 해결하기 위해 이 연구는 QKV-Softmax Layer-Fused (QKVS-LF) 구조를 도입하여 레이어 간 중간 데이터 저장을 최소화했고, Concurrent Transpose/Non-Transpose SRAM-CIM (LT-CTNT)으로 전치·비전치 연산을 동시에 수행해지연과 메모리 접근을 줄였다.

[그림 1] 제안한 hybrid nvProcessor의 전반적인 구조 및 QKVS LF의 동작 설명

또한 ReRAM-CIM에는 Dynamic Input Sign Extension Encoding (DISEE) 기법을 적용해 입력 희소성을 높이고 불필요한 연산을 줄임으로써 nvCIM의 높은 에너지 소모를 완화하였다. 22nm 공정으로 제작된 칩은 MobileViT 및 MobileNet 벤치마크에서 시스템 수준

41.8 TFLOPS/W의 에너지 효율과 ImageNet 정확도 74.5%를 달성했으며, 기존 nvProcessor 대비 1.9배 높은 성능 지표 (FoM)를 기록하였다. 이 논문은 작은 용량의 엣지 디바이스에서 Transformer를 실용적으로 가속할 수 있는 nvCIM 설계 전략을 제시했다는 점에서 중요한 의미를 가진다.

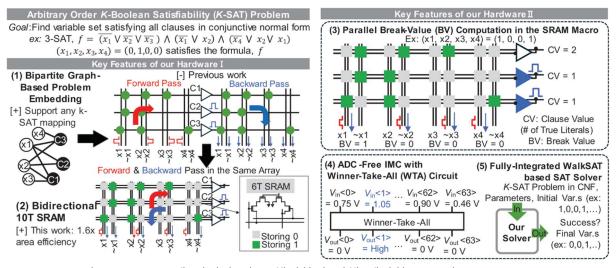

[그림 2] 제안한 2b-intra LT-LCC 와 DISEE 설명

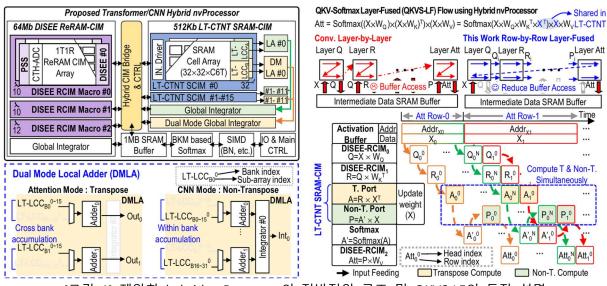

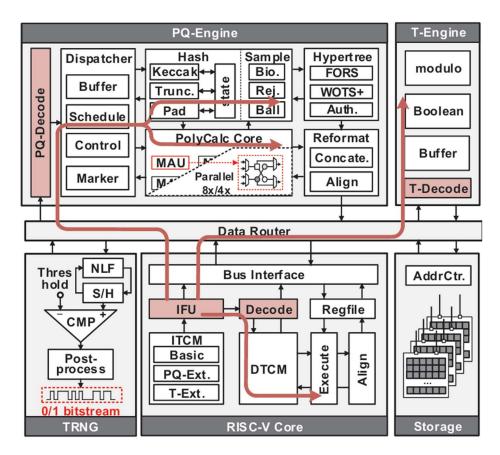

**#C17-4**는 UCSB와 1QBit이 공동으로 발표한 혼성 신호(Mixed-Signal) CIM 기반 SAT Solver로, 기존 3-SAT 전용 하드웨어를 넘어 임의 차수의 K-SAT 문제까지 직접적으로 해결할 수 있는 구조를 제시한 것이 가장 큰 특징이다.

[그림 1] K-SAT 문제 정의와 이를 해결하기 위해 제안한 work의 주요 feature들

핵심은 10T 양방향 SRAM 셀을 이용해 한 배열 내에서 절 (clause) 평가와 gradient/break-value 계산을 동시에 수행할 수 있도록 하였고, 이를 바탕으로 원샷(one-shot) 방식의 병렬 break-value 연산을 구현해 WalkSAT 알고리즘을 고속으로 실행할 수

있게 했다. 또한 아날로그 Winner-Take-All 회로를 도입해 promising 변수를 ADC 없이 선택 가능하도록 설계, 면적과 전력 효율을 높였다. 55nm 공정으로 제작된 칩은 최대 64 변수 문제까지 검증되었으며, 무작위 3-SAT 문제에서는 기존 ASIC 솔버 대비 약 10배, 4-SAT·5-SAT와 같은 고차수 문제에서는 최대 200배 빠른 연산 속도를 기록했다. 이 논문은 기존 디지털 혹은 3-SAT 전용 가속기의 한계를 넘어, 고차수 NP-hard 문제를 네이티브 하게 처리할 수 있는 범용 SAT 하드웨어 솔버로 CIM을 확장했다는 점에서 중요한 의의 를 가진다.

### 저자정보

#### 박은빈 박사과정 대학원생

● 소속 : 포항공과대학교

● 연구분야 : 임베디드 시스템 및 지능형 반도체

• 이메일 : eunbin@postech.ac.kr

● 홈페이지:

https://sites.google.com/view/epiclab/member/ebpark

한국과학기술원 전기및전자공학부 석사과정 권재훈

#### **Session C23 Innovatie Computing Systems**

이번 2025 IEEE VLSI의 Session C23은 Innovatie Computing Systems라는 주제로 총 4편의 논문이 발표되었다. 이 세션에서는 양자암호용 SoC, multi-node system 보호용 TIME architecture가 제안되었고, privacy와 security용 하드웨어에 중점을 두었다.

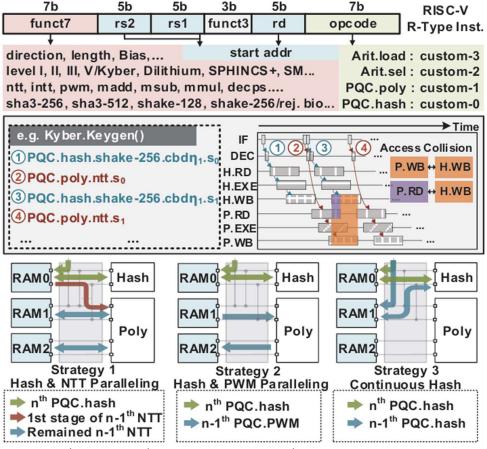

#C23-3 본 논문은 NIST의 최신 Federal Information Processing Standards (FIPS)를 지원하는 최초의 RISC-V 기반 양자암호용 SoC를 제안한다. SoC의 특징은 크게 3가지가 있고, 첫 번째는 RISC-V core와 deep-coupling된 post-quantum cryptographic (PQC) engine을 두고, dual-rail parallel scheduling으로 hash와 polynomial 연산 같은, 종류가 다른 primitive를 동시에 처리하여 pipeline활용을 극대화한 것이다. 두 번째로 Vectorized instruction-driven workflow를 통해 RISC-V custom instruction이 primitive를 직접 구동하는 것이다. 세 번째는 modulo add/sub/mult, Number theoretic transform(NTT)등의 primitive 연산을 fine-grained operator로 구현하여, 필요에 따라 reconstruction함으로써 여러 PQC scheme을 하나의 하드웨어로 지원하는 것이다.

그림 1에 전체 System architecture의 Top-level diagram이 나와있으며, RISC-V core, PQC engine(PQ-engine), traditional cryptographic engine(T-engine), TRNG, memory blocks 등으로 구성된 것을 확인할 수 있다. System은 그림에 적색으로 표시된 3가지 instruction pipeline execution path를 갖는데, 1번째 path는 Core path로서 RISC-V core 자체 실행 경로이다. control flow, parameter 초기화, pre/post-processing을 담당하며 2개의 64 KB globally-shared TCM을 사용하고 일반 RISC-V instruction으로 수행된다. 2번째 path는 PQ-engine path로서 Post-Quantum 전용 경로이다. PQC primitive인 hash/Keccak(SHAKE), sampler, polynomial/NTT, hypertree 등을 고속으로 처리하는 path이며, SRAM과 TRNG를 사용하고, 일반 instruction이 아닌 RISC-V custom extension instructions를 통해 수행된다. 3번째 path는 T-engine path로서 Traditional cryptographic path이다. SM2/SM3 등의 traditional한 algorithm을 처리하는 역할을 하며, core에서 신호를 주면 core와 병렬로 실행되는 2번째 path와 달리 3번째 pipeline에서 독립적으로 실행된다.

[그림 1] System architecture의 Top-level block diagram

SoC의 특징에 대해 더 자세히 설명하면, 일단 PQC algorithm은 여러 primitive로 분해될 수 있고, 이를 RISC-V vector extension instruction로 제어하는 것이 핵심이다. 이때 R-type custom instruction을 opcode expansion을 통해 확장하여 4가지 class로 분류하는데, 1번째로 algorithm, security level을 선택하여 scheme과 parameter set을 지정하는 역할을하는 Arit.sel, 2번째로 core와 engine간 또는 memory와 register간의 data transmission을 담당하는 Arit.load, 3번째로 NTT/INTT, modular mul/add 등의 polynomial 계산을 하는 PQC.poly, 마지막으로 hash와 sampling을 담당하는 PQC.hash이다. 이렇게 분류한 instruction들을 rearrange하면 run-time 중에도 다양한 PQC scheme으로 유연하게 reconfiguration할 수 있다. 특히 SoC의 1번째 특징으로 언급한 deep-coupling은 consecutive하게 배치된 PQC.poly와 PQC.hash를 parallel하게 실행한다는 뜻이다. parallel processing을 지원할 때 주의할 점 중 하나는, 하나의 resource를 동시에 접근할 수 없다는 점인데, 본 논문에서는 SRAM bank 분리 등의 data routing strategy를 적용하여 PQC.poly와 PQC.hash간의 time-overlapping execution에서 발생할 수 있는 문제를 해결했다. 이는 그림 2에서 Strategy 1, 2, 3로 표시돼있고, memory access collision을 효과적으로 방지한다는 것을 쉽게 알 수 있다.

SoC는 3가지의 PQC scheme(Kyber, Dilithium, SPHINCS+)에 대해 throughput과 energy efficiency를 측정하는 것으로 평가되었고, Kyber-512에서 최고 throughput 84.9 KOPS, 에

너지 1.82  $\mu$ J/op를 달성하였다. SoC의 spec은 28nm 공정으로 만들었을 때, core area가 2.11  $mm^2$ 이었고, gate count로 환산하였을 때 1.5M개 이고, 0.65–1.1 V 범위에서 50~800 MHz로 동작할 수 있었다.

[그림 2] RISC-V의 extension instruction과 data routing strategy

#C23-4 본 논문은 twin in-memory encryption/processing(TIME) macro를 설계해 Group Differential Privacy(GDP) + Spatial/Temporal Ensemble(STE) 를 하나의 memory macro에 통합하였다. 용어를 정리하면, GDP는 여러 node/data 간의 correlation을 고려하여 noise 를 강하게 injection하는 DP의 변형된 형태이다. 이것은 AloT 네트워크나 federated learning 등 여러 node가 있는 collective Al에서, node간의 correlation을 악용하는 공격으로부터 보호할 때 유용하다. 기존의 local differential privacy (LDP)는 single-node system 에서는 유효하지만, 여러 node가 있는 system에서는 취약하므로 본 논문에서 GDP를 도입한 것이다. STE는 여러 model에서 추론한 결과인 Spatial ensemble과, 동일 입력에 대해 시간적으로 여러 번 추론한 결과인 Temporal emsemble을 majority voting을 통해 결합하여, encryption/noise로 인한 정확도 손실을 완화하는 ensemble이다. ensemble은 여러 decision making model의 출력을 결합하여 하나의 예측을 만드는 방법이다.

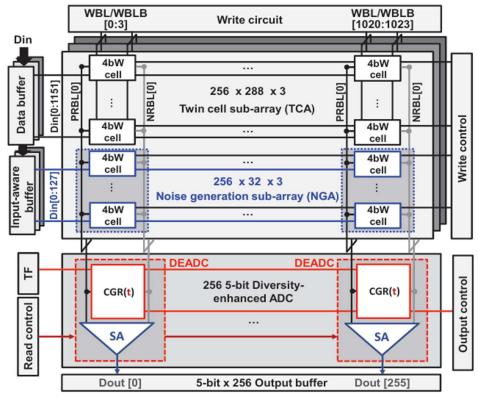

[그림 3] TIME의 전체 architecture

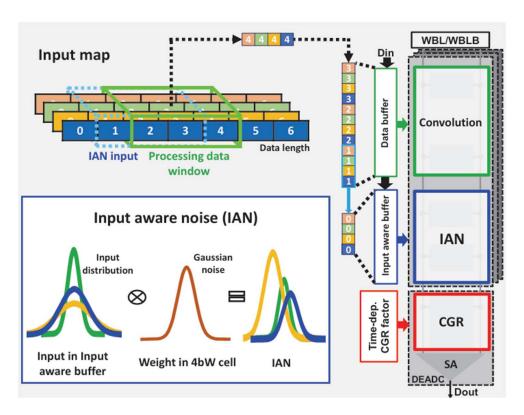

그림 3에 TIME의 architecture가 나와있고, 1Mb SRAM array, twin cell sub-array (TCA), noise generation sub-array (NGA), diversity-enhanced ADC (DEADC)와 peripheral circuit으로 구성된 것을 확인할 수 있다. TCA는 weight를 저장하면서 동시에 in-memory multiply를 수행하는 연산용 subarrya이다. 더 구체적으로는, 3개의 model fusion group으로 구성되어 있고, 각 group은 256×288개의 SRAM unit cell에 signed 4-bit weights(4bW)를 저장하고, 각 4bW unit cell은 3×4 subthreshold-MOS transistor array로, 4-bit input(4bIN) 과 4bW의 multiply를 수행한다. NGA는 간단하게 GDP용 noise를 생성하는 역할을 하며, TCA와 동일한 unit cell을 쓰지만 256×32개의 4-bit random weights를 저장해 noise generation에 활용한다. DEADC는 bit-line current 누적, SA, comparator로 이어지는 inmemory ADC이다. 즉, 같은 bit-line에 흐르는 전류를 누적하고, current mirror-based sense amplifier(SA)의 adjustable current gain ratio(CGR)로 scailling한 뒤 comparator로 양자화하는 역할을 한다. CGR을 사용하는 이유는 dynamic range/robustness를 확보하기 위해서이다.

TIME의 architecture의 mode는 크게 GDP encryption mode, STE mode가 있고 둘은 consecutive한 pipeline 단계를 거친다. GDP encryption mode에서는 Gaussian noise를 크고 sparse하게 만들기 위해 두 가지 방법을 사용한다. 1번째로, Input-Aware Noise(IAN)로 NGA에 저장된 random weights와 input-aware buffer의 input 일부를 mult&add하여 추가 RNG 없이 Gaussian에 가까운 decorrelated noise를 생성한 것이다.

[그림 4] GDP encryption mode의 datapath

2번째로, time-controlled CGR로 DEADC의 CGR을 time축으로 바꿔가며 5-bit output encoding 중 noise 변동성을 더 키운 것이다. 두 방법을 결합하여 SA만 쓸 때보다 Gaussian noise distribution 범위를 약 120%들렸다. 구체적인 GDP encryption mode의 datapath는 그림 4에 나와있다. STE mode는 정확도를 회복하기 위해 처리하고, 추론하는 mode이다. 3개의 TCA가 하나의 DEADC로 연결되어 Spatial ensemble을 구현하고, CGR을 같은 입력에 대해 여러 번 처리하여 Temporal ensemble을 구현했으며 이 결과를 voting 과 averaging을 통해 결합했다. 마지막으로 TIME architecture의 전체적인 흐름은 다음과 같다. Input - GDP noise injection(IAN + CGR) - In-Memory 연산(TCA/DEADC) - STE(Spatial+Temporal) - Voting - Output

#### 저자정보

#### 권재훈 석사과정 대학원생

● 소속 : 한국과학기술원 전기및전자공학부

• 연구분야 : Digital Circuit Design, ECC Hardware Design

이메일 : jhkwon@ics.kaist.ac.kr홈페이지 : https://ics.kaist.ac.kr/

포항공과대학교 반도체대학원 박사과정 박은빈

#### **Session 1 CIM and Quantum-inspired Computing**

이번 VLSI 2025의 Session C1 CIM and Quantum-inspired Computing은 인메모리 컴퓨팅의 확장성과 양자 영감형 아키텍처의 진화를 동시에 보여준 세션이었다. 발표된 연구들은 초미세공정 기반의 디지털 CIM부터 뉴로모픽 SNN 전용 구조, 그리고 대규모 이징머신까지 폭넓게 다루며, 공통적으로 데이터 이동 최소화와 계산 효율 극대화를 목표로하고 있었다. 특히, 최근의 요구인 LLM·SNN과 같은 응용 특화 과제와 NP-hard 최적화문제를 겨냥해, CIM은 더 높은 정밀도와 재구성 가능성을 확보하고, 이징 머신은 대규모스핀 연결성과 멀티칩 확장성을 통해 기존 한계를 뛰어넘고자 했다. 종합적으로 이번 세션은 CIM이 범용 가속기에서 응용 맞춤형 설계로 확장되고, 양자 영감형 접근이 실용적인 최적화 솔루션으로 자리잡아가는 흐름을 잘 보여주었다.

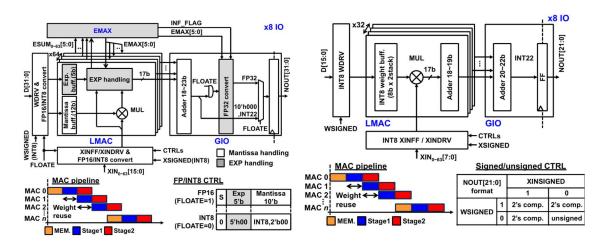

#C1-1은 TSMC 연구팀에서 발표한 3nm 공정 기반 SRAM Digital-CIM Compiler로, 기존 CIM과 달리 INT8과 FP16을 모두 지원하여 범용성과 유연성을 크게 확장한 것이 특징이다. 특히 FP16 연산에서 기존의 Alignment-First (AF) 방식 대신 Multiply-First (MF) 방식을 채택해 연산 정확도를 크게 개선하였으며, weight update를 주기당 여러 번 수행하는 multi-weight update per cycle 기법을 통해 메모리 대역폭 병목을 완화하고 활용도를 극대화하였다.

[그림 1] DCIM complier design의 전반적인 구조 및 동작원리

이러한 구조적 최적화 덕분에 INT8 모드에서 124.6 TOPS/W, FP16 모드에서 28.6 TFLOPS/W라는 세계 최고 수준의 에너지 효율을 달성하였다. 다만 상대적으로 간단한 벤치마크 환경에서의 검증에 머물렀다는 점은 아쉬움으로 남지만, 초미세공정 기반 범용 CIM이 실용화 단계에 진입했음을 보여주는 대표적 성과라 할 수 있다.

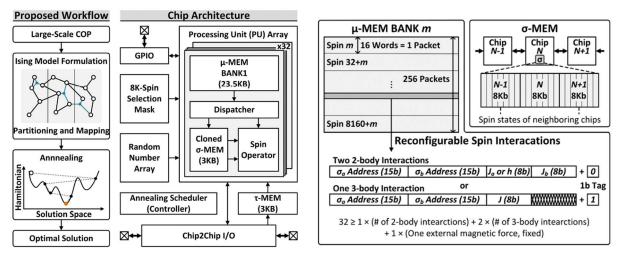

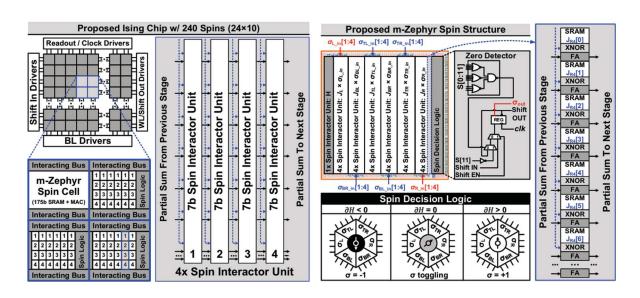

#C1-4는 POSTECH에서 발표한 28nm 공정 기반 8K-Spin Ising Machine IC로, 기존 이징 머신들이 주로 2체 상호작용(two-body)에 한정된 것과 달리 최대 31개의 2·3체 상호작용(many-body interactions)을 지원하는 것이 큰 특징이다. 또한 다수 칩을 직렬로 연결해 사실상 무한 확장이 가능한 limitless 1D multichip extension 구조를 도입해, 단일 칩의 한계를 넘어 대규모 최적화 문제를 직접 풀 수 있도록 설계되었다. 칩 내부에서는 σ-MEM과 μ-MEM을 기반으로 스핀 상태와 상호작용을 병렬적으로 처리하며, 스토캐스틱 셀룰러 오토마타(SCA)와 비율 제어 병렬 어닐링(RPA) 알고리즘을 지원해 빠른 수렴을 가능하게 했다. 실제 측정에서는 4개의 칩을 연결해 총 32,760 변수를 포함하는 대규모 3SAT 문제를 풀어내며, 기존 이징 머신 대비 문제 규모와 확장성에서 가장 앞선 성능을 입증하였다. 다만 복잡한 상호작용 지원을 위해 비교적 큰 하드웨어 자원이 요구된다는 점은한계로 남지만, NP-hard 문제 해결을 위한 양자 영감형 컴퓨팅의 실질적 확장 가능성을 보여준 점에서 중요한 성과라 할 수 있다.

[그림 1] 본 논문에서 제안한 대규모 최적화문제를 풀기위한 workflow 및 Ising model 3차 하드웨어 구현

#C1-5는 UCSB와 KAIST가 공동으로 발표한 m-Zephyr Digital In-Memory Ising Chip으로, 기존 이징 머신의 제한된 연결성을 극복하기 위해 수정된 3D Zephyr 토폴로지를 도입하여 스핀 당 24개의 상호작용을 지원하는 것이 특징이다. 이는 lattice나 King's graph 기반 구조보다 훨씬 복잡한 문제를 직접적으로 매핑할 수 있게 하여, 재구성 가능성과 표

현력을 크게 높였다. 또한 7비트 정밀도의 완전 디지털 인메모리 연산을 통해 정확도를 유지하면서도 <180ns의 빠른 수렴 시간과 <350nJ의 초저전력 동작을 달성하였다. 실제 측정 결과, 기존 Metropolis 알고리즘 대비 106배 빠른 문제 해결 속도와 더 낮은 평균 Hamiltonian 값을 보여주며, NP-hard 최적화 문제에서의 실효성을 입증하였다. 다만 65nm 공정 기반이라 최신 초미세공정보다 집적도는 낮지만, 연결성·정밀도·에너지 효율의 균형을 모두 잡은 디지털 이징 머신의 진화형 아키텍처라는 점에서 의의가 크다.

[그림 1] 제안한 m-Zephyr Ising chip의 전반적인 구조 및 schematic diagram

#### 저자정보

#### 박은빈 박사과정 대학원생

● 소속 : 포항공과대학교

● 연구분야 : 임베디드 시스템 및 지능형 반도체

● 이메일 : eunbin@postech.ac.kr

● 홈페이지:

https://sites.google.com/view/epiclab/member/ebpark

한국과학기술원 전기및전자공학부 석사과정 권재훈

#### **Session C30 Cryo-CMOS Circuit**

이번 2025 IEEE VLSI의 Session C30은 Cryo-CMOS Circuit이라는 주제로 총 4편의 논문이 발표되었다. 이 세션에서는 cryogenic 환경에서 동작하는 fully-integrated 4-channel Frequency-Division-Multiplexing (FDM) transmon qubit state readout ASIC과 dual-stage injection-locked oscillator(IL-DCO)로 구성된 cryo-CMOS signal selector 등을 제안하였는데, 두 circuit 모두 cyro-CMOS의 특징을 이용한 power comsuption을 줄이는 것에 중점을 두었다.

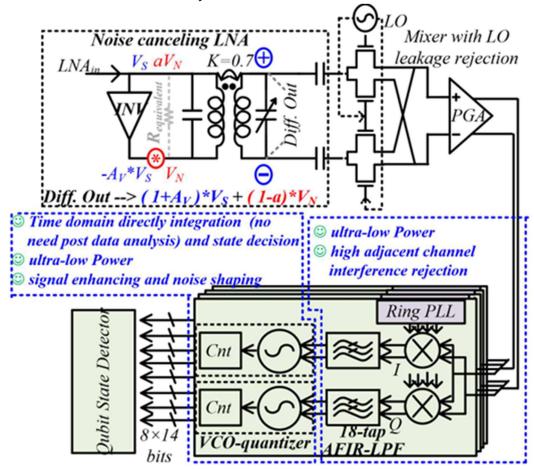

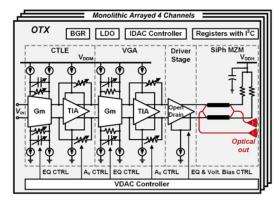

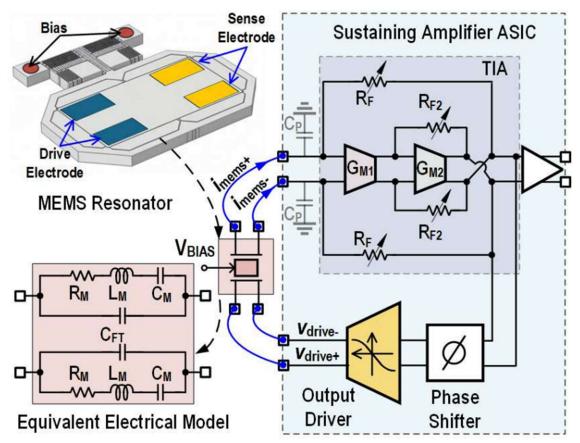

#C30-3 본 논문에서는 cryogenic 환경에서 동작하는 fully-integrated 4-channel Frequency-Division-Multiplexing (FDM) transmon qubit state readout ASIC을 제안하였다. Cryogenic CMOS ASIC은 표준 CMOS 공정으로 만든 ASIC을 극저온인 cryogenic 온도에서도 안정적으로 동작하도록 설계한 chip이다. 본 논문에서는 이러한 cryogenic CMOS ASIC의 특성을, 양자컴퓨팅의 대규모 확장에서 일어나는 문제점인 배선, I/O 병목의 해소에 이용하였다. 이전 연구는 Cryogenic CMOS ASIC을 일부에만 적용하여 여전히 전력 소모가 높으므로, 본 논문은 더 낮은 readout 전력을 달성하기 위한 연구를 한 것이다.

Cryo-CMOS Fully-integrated 4 Channel FDM qubit state readout architecture는 크게 3가지 특징을 가지고 있는데, 1번째는 Two-step down-conversion sliding-IF를 통해 high-frequency quadrature down-mixer가 요구하는 전력소모를 절감한 것이다. 구체적으로는 기존 수신기는 quadrature down-mixer를 사용하여 한 번에 frequency를 down-conversion하여 전력 소모가 컸는데, sliding-IF 구조로 바꿔서 frequency를 한 번에 down-conversion하지 않고 Intermediate frequency를 중간에 거쳐서 two-step으로 down-conversion하여 전력 소모를 줄인것이다. 2번째는 Narrow-band zero-IF topology에 18-tap AFIR을 결합하여 FDM의 adjacent channel interference를 줄인것이다. 기존 FDM readout에서는 adjacent channel 누설로 인해 SNR이 저하되는 문제가 있었는데, AFIR(Analog FIR) LPF(low pass filter)가 narrow한 band만 통과시켜서 channel selectivity를 높인 것이다. 이때 zero-IF는 direct-conversion 또는 homodyne이라고도 불리며 한 번의 mixing으로 baseband로 down-conversion하는 구조이며, 1번째에서 얘기한 IF에서 basedband로 frequency를 내릴 때 zero-IF 구조를 사용한 것이다. 3번째는 VCO-based analog signal conversion으로 time-domain state decision을 수행해 noise shaping 장점을

얻고 직접 qubit 상태를 판독한 것이다. 기존에는 ADC입장에서 FDM의 대역폭을 한 번에 봐야하므로 고속, wideband를 지원해야 하는 부담이 있었는데, 본 논문에서는 VCO를통해 입력 전압을 frequency 변화로 mapping하여 counter로 period를 측정하는 것으로바꿔서, ADC를 사실상 대체하여 system의 부담을 낮춘 것이다.

[그림 1] fully-integrated 4-channel FDM homodyne demodulation readout receiver의 architecture

그림 1에 fully-integrated 4-channel FDM transmon qubit state readout ASIC의 전체 architecture가 나와있고, 크게 RF-(Mixer1)-IF-(IF Mixer2)-zero-IF의 구조를 갖는다는 것을 알 수 있다. 구조에 대해 살펴보면, 먼저 좌측 상단의 Noise canceling LNA(low noise amplifier)는 입력으로  $V_S + V_N$ 이 들어오고, transformer를 통해 differential 신호로 변환하며 신호( $V_S$ )는 증폭하고 noise( $V_N$ )는 낮추는 역할을 한다. 이때의 식은  $(1+A_v)V_S+(1-a)V_N$  이다. 우측 상단에 나와있는 Mixer with LO(Local Osillator) leakage rejection과 PGA(Programmable Gain Amplifier)는 LO leakage를 줄이기 위한 architecture이며 self-mixing과 DC-offset 등을 줄이는 역할을 한다. 이때 LO leakage는 mixer의 LO signal이 RF-IF path로 leakage되는 현상이다. 또한 여기 있는 mixer는 1번째 down-conversion으로 수백 MHz 대역의 IF로 내리고, PGA가 필요한 gain만큼 gain을 보정하는 역할도 겸한다. 우측 하단에 나와있는 Ring PLL은 4개의 on-chip PLL로 구성되고, 1번째 mixing 후에 4개의 channel에서 channel마다 IF frequency가 조금씩 다른데, 이것을 딱 맞춰주는 역할

을 한다. 이 과정을 거쳐야 AFIR-LPF가 narrow bandwidth로 adjacent channel interference를 효과적으로 rejection할 수 있다. Ring PLL바로 아래의 IF mixer는 2번째 down-conversion으로 각 channel을 baseband 근처인 zero-IF로 정밀하게 낮춰주는 역할을 한다. IF mixer의 바로 왼쪽에 있는 18-tap AFIR-LPF는 FDM adjacent channel interference를 효과적으로 제거하여, 뒷 단의 dynamic range와 power등의 constraint를 완화시킨다. 이때 area와 power를 줄이기 위해, time-interleaved 방식으로 하나의 AFIR-LPR를 4-channel이 공유한다.

[그림 2] VCO-quantizer와 time-domain integration

다음으로 그림 하단의 VCO-quantizer는 baseband 전압을 Gm(transconductance) cell을 이용하여 전류로 바꿔서 current-biased ring-VCO에 누적하고, 그 결과 생기는 frequency/phase 변화를  $T_{int}$ 동안 counter로 세어 14-bit으로 encoding하여 이를 직접 판정하는데 사용한다. 이 과정은 그림 2에 상세히 나와있고, 우측 상단의 Quantizer와 Register bank를 통해 각 phase signal의 edge를 감지하여, counter가  $T_{int}$ 동안 세서 14-bit code로 encoding되는 것을 확인할 수 있다. VCO-quantizer의 output은 8\*14-bit인데, 이는 channel마다 I,Q 2가지 path가 있으므로 8개의 14-bit값이 출력되기 때문이다. 마지막으로 그림 1 좌측 하단의 Qubit State Detector는 counter 출력을 직접 비교하여 qubit 상태를 분류하는 역할을 한다. 그림에 표시된 것처럼 복잡한 digital channelizer나 high resolution ADC등의 post data anlysis가 별도로 필요 없다는 것을 알 수 있다.

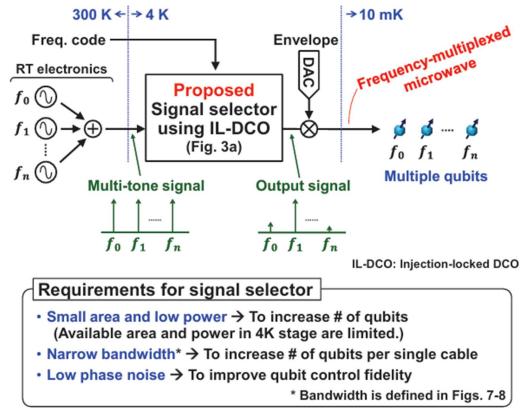

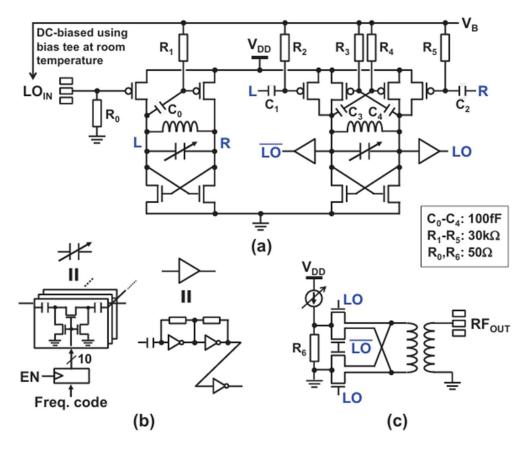

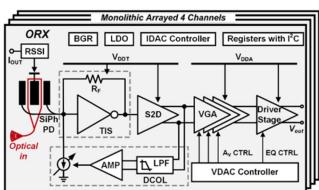

#C30-4 본 논문에서는 dual-stage injection-locked oscillator(IL-DCO)로 구성된 cryo-CMOS signal selector를 제안하였다. 현재 양자컴퓨터에서는 qubit마다 unique한 control frequency를 가지고 있어서, refrigerator의 cryogenic stage에 oscillator를 여러 개 둬야 하고, 이로인해 power 소모가 큰 문제가 있다. 따라서 논문에서는 selector를 통해 multitone microwave 신호에서 원하는 단일 tone만 추출해서 qubit 제어에 쓰고 power 소모를 줄인다는 idea이다.

[그림 3] 제안된 cyro-CMOS signal selector architecture

그림 3에는 논문에서 제안한 cyro-CMOS signal selector architecture가 나와있고, 그림의 왼쪽에서 보이는 것처럼 RT(300K)에서 여러 oscillator가 만든 multi-tone microwave를 single 케이블로 CT(4K)까지 내린다. 그 다음 IL-DCO based signal selector가 지정된 single-tone만 선택하여, envelope DAC와 mixer를 통해 pulse shaping한 후 10mK의 multiple qubits에 공급하는 frequency-multiplexed qubit control을 하는 idea가 설명된 것이다. 논문에서 제안한 signal selector는 5.7~7.5 GHz 대역을 목표로 한 dual-stage IL-DCO(Injection-Locked Digitally Controlled LC Oscillator) 구조이며 그림 4에 selector의 circuit implementation이 나와있다. (a)는 Dual IL-DCO이며 핵심 circuit이다. 먼저 1번째 IL-LDO에서 cross-coupled LC tank가 injection-locking으로 resonance  $f_0'$  에 가장 가까운 입력 tone에 lock시킨다. 이때 L, R node는 1번째 DCO의 differntial output이고, C1~C4를 통해 2번째 DCO에 전달된다.

[그림 4] 제안된 selector의 circuit implementation

2번째 IL-DCO에서는 1번째와 같은  $f_0'$ 에 맞춰져서, 선택되지 않은 tone을 weak하게 만들어서, select된 tone을 더 refine한다. signal flow는 다음과 같다. LOIN(multi-tone) - 1번째 IL-DCO가  $f_0'$  근처 tone에 lock - L/R - 2번째 IL-DCO injection&refinement - mixer에서 LO로 gating - balun - RFOUT(single-tone). 실험은 single-tone 입력의 frequency relationship evaluation, 4-tone 입력의 tone selection, 2-tone에서의 SFDR 측정으로 크게 3가지 경우에 대해 진행되었으며, 각각의 실험으로 frequency를 정밀하게 선택할 수 있는지. multi-tone을 실제로 support하는지, SFDR requirement를 만족하는지를 증명한 것이다.

#### 저자정보

#### 권재훈 석사과정 대학원생

● 소속 : 한국과학기술원 전기및전자공학부

• 연구분야 : Digital Circuit Design, ECC Hardware Design

● 이메일 : jhkwon@ics.kaist.ac.kr

• 홈페이지: https://ics.kaist.ac.kr/

경북대학교 전자전기공학부 박사과정 박승현

#### **Session 10 AI Accelerators 1**

VLSI 2025 10 세션의 네 편 논문은 영상 처리와 엣지 컴퓨팅, 온디바이스 학습, 로보틱스시스템 등 차세대 응용을 위한 새로운 아키텍처적 접근을 제시한다. 10-2는 코덱과 후처리를 통합한 비디오 프로세서를 통해 영상 스트리밍 전반의 효율을 근본적으로 개선할수 있음을 보여주었다. 10-3은 하이퍼디멘셔널 컴퓨팅을 활용해 지속 학습이 가능한 온디바이스 가속기를 구현함으로써, 에너지 효율적인 적응형 학습의 가능성을 제시했다. 10-4는 타일 기반의 유연한 가속기 구조를 통해 워크로드 변화에 실시간으로 대응할 수있는 엣지 컴퓨팅 플랫폼의 새로운 방향을 제안하였다. 마지막으로 10-5는 로보틱스 응용에 특화된 이종 SoC를 설계해, 복잡한 인지 및 제어 파이프라인을 하나의 칩에서 통합적으로 처리할 수 있는 가능성을 열었다.

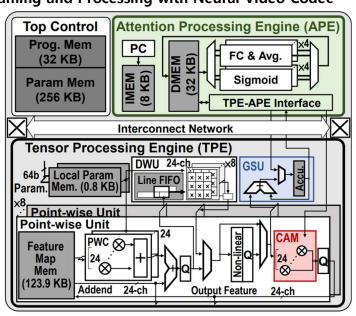

# #10-2 NuVPU: A 4.8~9.6 mJ/frame Progressive NTT-based Unified Video Processor for Stable Video Streaming and Processing with Neural Video Codec

[그림 1] Overall System Architecture

본 논문은 Neural Video Codec (NVC)을 기반으로, 영상 스트리밍과 후처리를 동시에 지원하는 통합형 비디오 프로세서 NuVPU를 제안한다. 기존 연구들은 주로 후처리에 초점

을 맞춰 코덱 정보 활용이 미흡했는데, 저자는 코덱 내부의 모션 벡터 등 중간 정보를 적극적으로 활용하여 전체 파이프라인 효율을 높이고자 하였다.

핵심 기여는 세 가지이다. 첫째, Selective Convolution-mode Neural Engine(SCNE)은 공간 도메인과 NTT 도메인 연산을 상황에 따라 전환하며, 이를 통해 평균 1.69~3.35배의 처리량 향상을 달성하였다. 둘째, Progressive NTT Unit (PNTU)는 불필요한 연산과 메모리 접근을 줄여 도메인 변환 시 연산량을 44.8%, 메모리 접근을 80% 절감하였다. 셋째, Frequency-aware Compressor (FAC)와 Adaptive Tile Scheduler (ATS)는 warping 기반 프레임 재활용 과정에서 발생하는 EMA를 81.3%까지 줄였다.

28nm 공정으로 제작된 칩은 최대 250MHz에서 동작하며, 4.89.6 mJ/frame의 에너지 소모로 36.9 TOPS/W의 탁월한 에너지 효율을 달성하였다. 이는 기존 비디오 프로세서 대비 9.22.3배 향상된 수치다. 또한 4K 영상 스트리밍에서 0.37 SSIM, 0.7 PSNR의 품질 향상을 입증하며, 실제 응용에서의 우수한 성능을 보여주었다.

본 연구는 코덱과 후처리를 통합적으로 고려하여, NVC 기반 차세대 영상 스트리밍에 적합한 새로운 프로세서 아키텍처를 제시한다는 점에서 의의가 크다. 특히 도메인 변환 최적화와 메모리 효율화 기법을 결합해, 실시간 고해상도 영상 서비스의 연산·전력 병목을 근본적으로 해결할 수 있음을 입증했다는 점이 인상적이다.

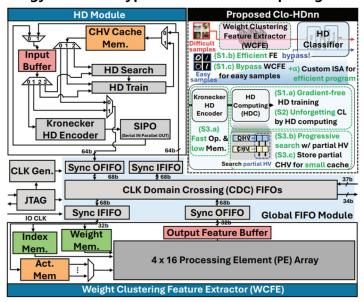

#10-3 Clo-HDnn: A 4.66 TLOPS/W and 3.78 TOPS/W Continual On-Device Learning Accelerator with Energy-efficient Hyperdimensional Computing via Progressive Search

[그림 2] Proposed Clo-HDnn Architecture and Key Features

본 논문은 지속 학습 (Continual Learning, CL)을 지원하는 온디바이스 학습 가속기 Clo-HDnn을 제안한다. 기존 온디바이스 학습은 그래디언트 기반 학습으로 인한 높은 연산량과 메모리 소모, 그리고 새로운 데이터 학습 시 기존 지식을 잃는 문제 (catastrophic forgetting)를 겪어왔다. 저자는 이러한 한계를 극복하기 위해 뇌 영감을 받은 하이퍼디멘셔널 컴퓨팅 (HDC)을 도입하였다.

핵심 아이디어는 세 가지이다. 첫째, Gradient-free HDC 기반 학습을 적용해 연산 복잡도를 크게 줄이고, 필요 시 저비용의 Weight Clustering Feature Extractor (WCFE)를 통해 효율적인 특징 추출을 수행한다. 둘째, Kronecker HD 인코더와 프로그레시브 서치 (progressive search) 기법을 통해 입력 데이터를 부분적으로만 인코딩·탐색해 불필요한 연산을 줄이면서도 정확도를 유지한다. 셋째, 듀얼 모드 동작을 지원하여 간단한 데이터 셋에서는 특징 추출 과정을 생략하고, 복잡한 데이터셋에서는 정교한 추출을 수행함으로 써 상황에 맞는 유연한 학습이 가능하다.

이를 통해 Clo-HDnn은 기존 CL 가속기의 한계를 넘어서, 지속적 적응 학습과 지식 보존을 동시에 달성할 수 있는 새로운 아키텍처적 패러다임을 제시한다. 본 연구는 온디바이스 환경에서 에너지 효율적이고 경량화된 CL 구현 가능성을 입증하며, 향후 IoT, 웨어러블, 로보틱스 등 동적 환경에서의 지능형 시스템 설계에 중요한 기여를 한다.

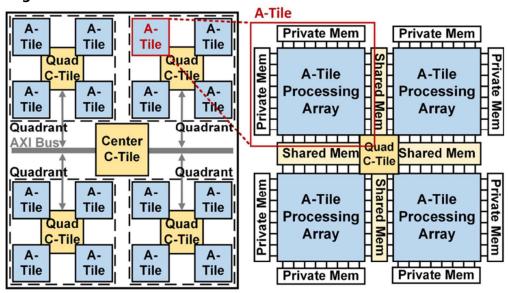

#10-4 EVA: A 16mm2 1.54TFLOPS Tiled-Based Accelerator for Evolvable Edge Computing

[그림 3] Hierarchically Connected EVA Architecture

본 논문은 엣지 컴퓨팅의 빠르게 변화하는 워크로드에 대응하기 위해 설계된 타일 기반 가속기 EVA를 제안한다. 기존의 도메인 특화형 가속기는 특정 커널에는 최적화되어 있으나, 워크로드가 변화할 때 자원 활용도가 떨어지는 한계가 있었고, 반대로 CGRA 기반 구조는 유연성을 제공하지만 재구성이 느려 실시간 적응성에 제약이 있었다.

EVA는 이를 해결하기 위해 프로그래머블 PE 어레이 (A-Tile)와 RISC-V 기반 제어 타일 (C-Tile)을 결합한 이종 타일 아키텍처를 도입하였다. A-Tile은 다양한 연산 커널을 높은 활용도로 수행할 수 있고, C-Tile은 수십~수백 ns 수준에서 빠른 런타임 적응 및 재구성을 담당한다. 또한 분산 메모리 구조와 다층 인터커넥트 패브릭을 통해 데이터 이동의 효율성을 높였으며, 워크로드를 공간적/시간적 매핑으로 최적화할 수 있는 유연한 실행환경을 제공한다.

이러한 설계를 통해 EVA는 고성능·고밀도 연산과 동시에 실시간 적응성을 달성하였으며, 엣지 환경에서의 진화하는 다양한 작업을 단일 플랫폼에서 효율적으로 처리할 수 있는 가능성을 보여주었다. 본 연구는 엣지 컴퓨팅 아키텍처가 앞으로 성능과 유연성의 균형 을 어떻게 맞춰야 하는지를 제시하는 중요한 방향성을 제공한다.

#### 저자정보

#### 박승현 박사과정 대학원생

● 소속 : 경북대학교

● 연구분야 : 딥러닝 가속기 설계● 이메일 : ijjh0435@gmail.com

• 홈페이지 : https://ai-soc.github.io/

한양대학교 신소재공학과 석박통학과정 송충석

#### Session 13 Al Accelerators 2

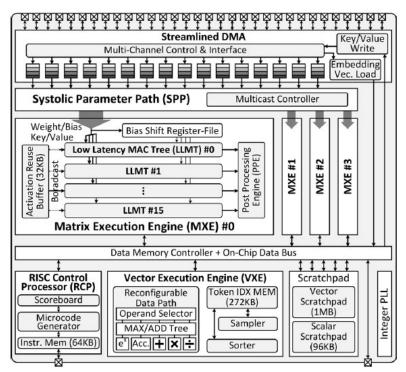

이번 2025 IEEE VLSI의 Session 13은 AI Accelerators 2라는 주제로 총 4편의 논문이 발표되었다. 현재 가장 활발히 연구되고 있는 transformer 구조를 가속하기 위한 하드웨어가 발표되었으며, #13-1은 디코더 기반 transformer, #13-2는 multi-task transformer, #13-3은 transformer 학습, #13-4는 diffusion 기반 transformer를 타겟으로 정하였다. 본 review에서는 #13-1, #13-2, #13-3을 review한다.

#13-1 논문에서는 Adelia라는 대규모 언어 모델을 가속하는 칩을 발표하였다. 디코더 기반 대규모 언어 모델의 추론은 prefill 단계와 decode 단계로 구분되며 prefill 단계에서는 높은 연산 집약도를, decode 단계에서는 메모리 접근 병목을 보이는 상반된 특성을 가진다. 이러한 특성으로 인해 기존 GPU에서는 메모리 대역폭 활용률과 연산 자원 활용률이 낮으며, 다른 전용 가속기들 또한 decode 단계에 최적화되었으나 prefill 처리에서 성능이 떨어지는 문제를 가지고 있다. 이러한 문제를 해결하기 위해 본 논문에서는 streamlined dataflow와 dual-mode parallelization을 제안하고 이를 Adelia에 탑재하였다. Streamlined dataflow는 외부 메모리와 연산 엔진 사이의 대역폭을 정확히 매칭시켜 주는 방법으로 데이터 이동 경로를 불필요한 버퍼링 없이 단순화함으로써 연산 엔진이 항상 메모리 대역폭에 맞춰 최대로 동작하도록 하는 구조다. 더불어 긴 context를 분산 처리하는 context mode와 여러 요청을 동시에 처리하는 batch mode를 적용한 Dual-mode parallelization을 Adelia에 구현하였다.

Adelia는 4nm CMOS 공정으로 제작되었으며, 면적은 5.28mm^2, 동작 전압은 0.65 – 0.9V, 최대 주파수는 1GHz이다. 측정 결과 GPU 대비 메모리 대역폭 효율은 1.59배, 처리량 효율은 2.51배 향상되었다. 그 결과 Llama-7B 추론에서 최대 latency를 35.1퍼센트 감소를 보여줌으로 인해 단일 최적화(decode 단계)에 집중했던 기존 연구 대비 더 균형 잡힌 성능을 보여주었다.

[그림 1] Adelia의 전체 하드웨어 구조

#13-2 논문에서는 최초의 multi-task transformer 가속기를 칩으로 제작한 결과를 발표하였다. Multi-task transformer는 "base task" 와 그에 대한 차이(delta)를 계산하는 "sub task" 구조를 활용하여 "sub task" 연산 시 base task를 기준으로 차이만을 활용하여 재연산하기 때문에 효율적인 네트워크로 주목받고 있다. 그러나 delta 행렬의 불규칙한 희소성, 빠른 전력/성능 변화, base task와 delta의 서로 다른 정밀도 요구로 인해 하드웨어 구현이 까다로운 문제가 있었다. 본 논문은 세가지 방식을 하드웨어에 적용해 multi-task transformer를 가속하였다: 첫번째는 block-wise structure sparsity를 도입하여 delta 행렬의 희소성에 제약을 가해 재 학습시켜 불규칙성을 완화시켰고, 두번째는 DVFS (dynamic voltage frequency scaling) 기법을 접목시켜 workload에 따른 빠른 전압 변환을 통해 효율적인 전력공급을 가능케 하였고, 마지막으로 mixed precision 연산을 적용해 base task를 INT8, sub task와 delta는 INT4/INT8, softmax 연산은 INT32로 수행하여 전력 소모를줄이면서 정확도를 유지시켰다.

제안된 칩은 22nm CMOS 공정으로 제작되었으며, 면적은 5.8mm^2를 차지하였다. 실제 multi-task 시나리오에서 평균적으로 sub-task는 41%에너지 감소와 68% 딜레이 감소를 달성했으며, DVFS 기법을 적용시켜 추가로 21.4%의 에너지 절감을 이루었다. 특히 sub task의 수가 증가할수록 base task 계산 비용이 분산되어 효율이 더 높아졌으며, 이는 기존 single-task transformer 가속기와 차별화되는 지점이라고 볼 수 있다.

[그림 2] 제안한 칩의 하드웨어 전체 구조.

#13-3 논문에서는 ASAP이라는 transformer 학습을 가속화할 수 있는 칩을 발표하였다. 기존 GPU에서 희소성을 포함한 네트워크를 학습시킬 때, 고정된 N:M 희소성 제약으로 인해 중간 단계의 희소성 수준을 적용하기 어려운 문제가 있다. 예를 들어, GPU에서 2:4 희소성만 (4개의 데이터 중 2개는 0으로 설정) 지원한다면, 중간 수준의 3:8, 5:8 희소성 등은 적용할 수 없다. 이를 해결하기 위해 ASAP은 다양한 N:M 희소성 연산을 지원함과 동시에 비대칭 정밀도를 동시에 지원하는 접근법을 제안하였다.